# Filière Systèmes industriels

Orientation Power & Control

# Travail de bachelor Diplôme 2017

# Romain Carreto

Conception et tests d'interfaces de puissance pour système d'imagerie médicale

Philippe Barrade

Romain Sahli

Date de la remise du rapport 18.08.2017 / 12h00

## Données du travail de diplôme Aufgabenstellung der Bachelorarbeit

FO 1.2.02.07.CB haj/11/01/2016

| Filière / Studiengang<br>SYND                                                    |                                                         | Année académique / Studienjahr 2016/2017                                                                                                                          | No TD / Nr. DA<br>pc/2017/55                                   |  |

|----------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|

| Manda<br>⊠<br>□                                                                  | ant / <i>Auftraggeber</i><br>HES—SO Valais<br>Industrie | Etudiant / Student Romain Carreto                                                                                                                                 | Lieu d'exécution / Ausführungsort  ☑ HES—SO Valais ☐ Industrie |  |

|                                                                                  | Etablissement partenaire<br>Partnerinstitution          | Professeur / Dozent Philippe Barrade                                                                                                                              | Etablissement partenaire Partnerinstitution                    |  |

| Travail confidentiel / vertrauliche Arbeit  ☐ oui / ja <sup>1</sup> ☐ non / nein |                                                         | Expert / Experte (données complètes)  Mr. Romain Sahli, EssentialTech, CODEV – EPFL, CM 1368, Station 10, 1015 Lausanne. +41 (0)21 693 6046, romain.sahli@epfl.ch |                                                                |  |

Titre / Titel

#### Conception et tests d'interfaces de puissance pour système d'imagerie médicale

Description / Beschreibung

Dans le cadre d'une collaboration avec un partenaire industriel, le Laboratoire d'Electronique Industrielle est en charge de réaliser un dispositif d'alimentation de système d'imagerie médicale. Ce dispositif doit incorporer les interfaces de puissance nécessaires à l'alimentation d'un tube à rayons-X et ses auxiliaires, à partir d'une alimentation monophasée basse-tension ou de cellules photovoltaïques. L'ensemble doit être organisé autour d'éléments d'accumulation d'énergie afin de garantir une autonomie donnée en cas de rupture de l'alimentation.

Le présent projet consiste à se focaliser sur un des modules de conversion à implémenter pour cette application, et comportera trois étapes principales :

- Analyse du système global, et du sous-système à développer. Définition et/ou analyse des spécifications relatives au module à développer.

- Mise en œuvre des procédures et outils de dimensionnement du sous-système. Dimensionnement et simulations de pré-validation.

- Prototypage du dispositif et tests.

#### Objectifs / Ziele

- Analyse de spécifications et dimensionnement d'un dispositif.

- Mise en œuvre et tests sur le module dimensionné.

- Remise d'un dossier technique complet et documentation.

| Signature ou visa / Unterschrift oder Visum                                          | Délais / Termine                                                           |  |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|

| Responsable de l'orientation / filière Leiter der Vertiefungsrichtung / Studiengang: | Attribution du thème / Ausgabe des Auftrags: 15.05.2017                    |  |

|                                                                                      | Présentation intermédiaire / Zwischenpräsentation 08 – 09.06.2017          |  |

| <sup>1</sup> Etudiant / Student :                                                    | Remise du rapport / Abgabe des Schlussberichts: 18.08.2017 / 12h00         |  |

|                                                                                      | Expositions / Ausstellungen der Diplomarbeiten: 30.08 – 31.08 – 01.09.2017 |  |

|                                                                                      | Défense orale / Mündliche Verfechtung:<br>Semaine 36 / Woche 36            |  |

Par sa signature, l'étudiant-e s'engage à respecter strictement la directive DI.1.2.02.07 liée au travail de diplôme.

Durch seine Unterschrift verpflichtet sich der/die Student/in, sich an die Richtlinie DI.1.2.02.07 der Diplomarbeit zu halten.

## Table des matières

| 1 | Intro | duction                                 | 3    |

|---|-------|-----------------------------------------|------|

| 2 | Cahi  | er des charges                          | 3    |

|   | 2.1   | Introduction                            | 3    |

|   | 2.2   | Description                             | 3    |

|   | 2.3   | Objectifs                               | 4    |

|   | 2.4   | Schéma fonctionnel                      | 4    |

|   | 2.5   | Spécifications et contraintes           | 4    |

|   | 2.6   | Tâches à réaliser                       | 5    |

|   | 2.7   | Planning prévisionnel                   | e    |

|   | 2.8   | Remarques                               | e    |

| 3 | Phas  | e 1 : Spécification                     | 7    |

|   | 3.1   | Choix de la topologie                   | 7    |

|   | 3.2   | Première sélection                      | 8    |

|   | 3.3   | Deuxième sélection                      | 8    |

|   | 3.4   | Synthèse et décision sur la topologie   | . 11 |

| 4 | Phas  | e 2 : Conception                        | . 16 |

|   | 4.1   | Système en boucle ouverte               | . 16 |

|   | 4.1.1 | Equations liés à la topologie           | . 17 |

|   | 4.1.2 | Formes d'ondes                          | 23   |

|   | 4.1.3 | Dimensionnement des éléments principaux | . 24 |

|   | 4.1.4 | Contrôle par simulation                 | . 31 |

|   | 4.1.5 | Valeurs numériques                      | . 33 |

|   | 4.1.6 | Modèles pour le calcul des pertes       | 35   |

|   | 4.2   | Régulation du dispositif                | 37   |

|   | 4.2.1 | Schéma de principe                      | . 38 |

|   | 4.2.2 | Régulation du courant de sortie         | 39   |

|   | 4.2.3 | Régulation du courant magnétisant       | 43   |

|   | 4.2.4 | Codage de la régulation                 | 48   |

|   | 4.3   | Synthèse de la phase de conception      | . 50 |

| 5 | Phas  | e 3 : Simulation                        | 50   |

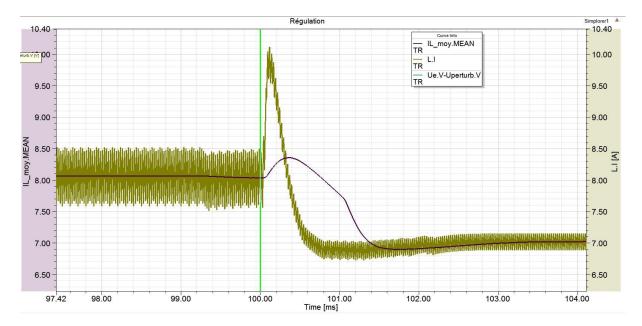

|   | 5.1   | Boucle fermée                           | 50   |

|   | 5.1.1 | Régulation du courant de sortie         | . 50 |

|   | 5.1.2 | Régulation du courant magnétisant       | . 52 |

|   | 5.1.3 | Saut de tension en entrée du dispositif | 53   |

| 6 | Phas  | e 4 : Intégration                       | 55   |

|   | 6.1   | Contraintes sur les composants          | . 55 |

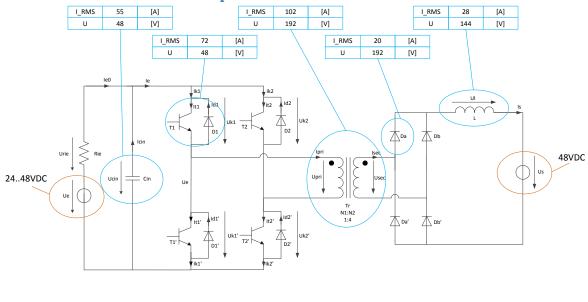

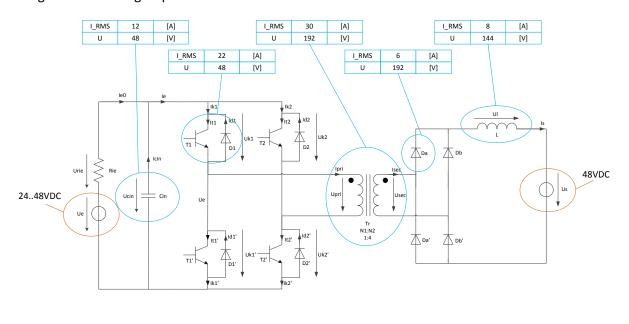

### Convertisseur DC/DC

|    | 6.1.1 | 1 Diodes du redresseur                  | 56 |

|----|-------|-----------------------------------------|----|

|    | 6.1.2 | 2 Interrupteurs                         | 56 |

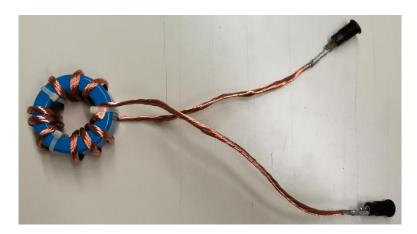

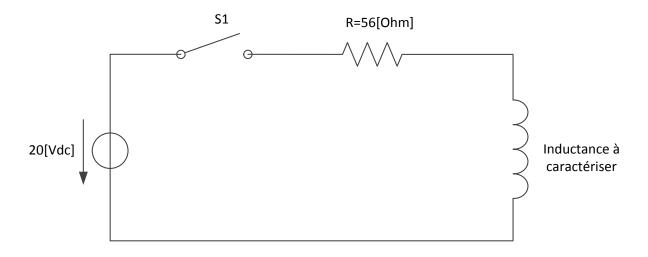

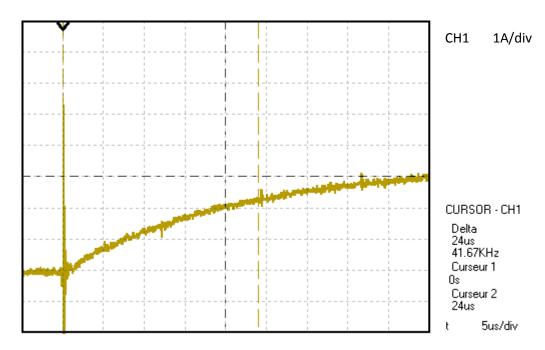

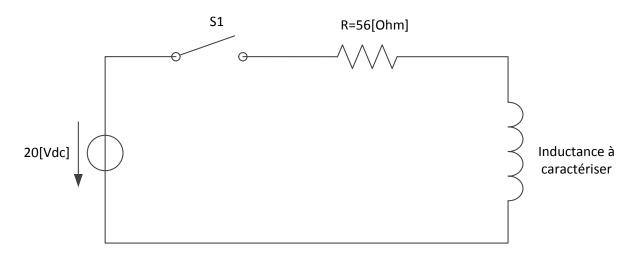

|    | 6.1.3 | 3 Inductance de sortie                  | 56 |

|    | 6.1.4 | 4 Transformateur                        | 59 |

|    | 6.1.5 | 5 Condensateur d'entrée                 | 65 |

|    | 6.1.6 | 6 Capteur de courant                    | 65 |

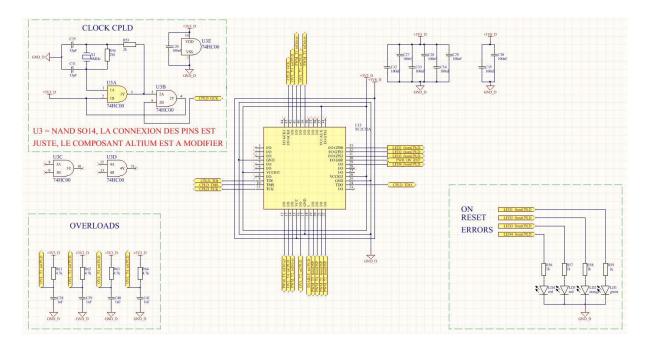

|    | 6.1.7 | 7 CPLD et autres composants actifs      | 65 |

|    | 6.2   | Calcul des pertes                       | 66 |

|    | 6.2.1 | 1 Diodes                                | 66 |

|    | 6.2.2 | 2 Interrupteurs                         | 66 |

|    | 6.2.3 | 3 Inductance                            | 66 |

|    | 6.2.4 | 4 Transformateur                        | 66 |

|    | 6.2.5 | 5 Rendement estimé                      | 66 |

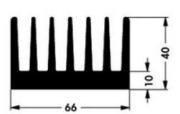

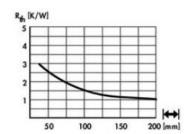

|    | 6.2.6 | 6 Dissipateur thermique                 | 67 |

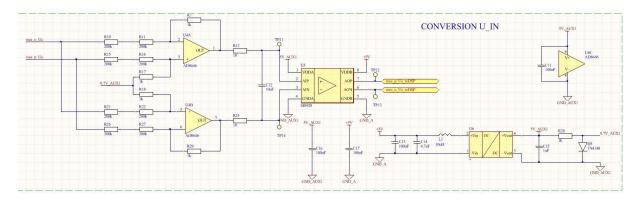

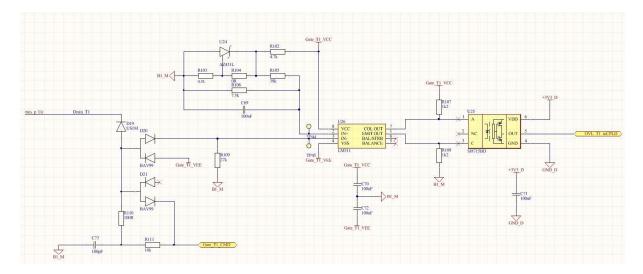

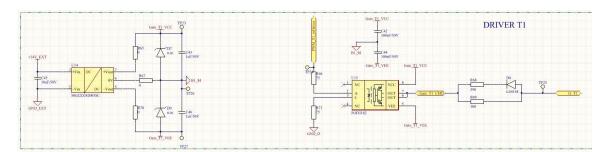

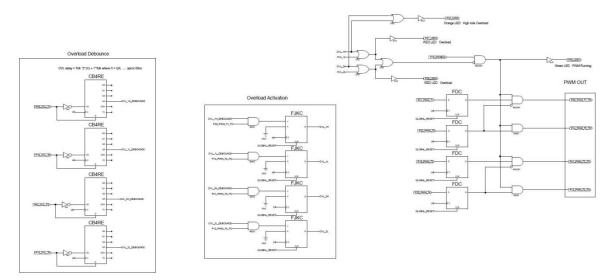

|    | 6.3   | Schémas électriques                     | 69 |

|    | 6.3.2 | 2 Routage                               | 76 |

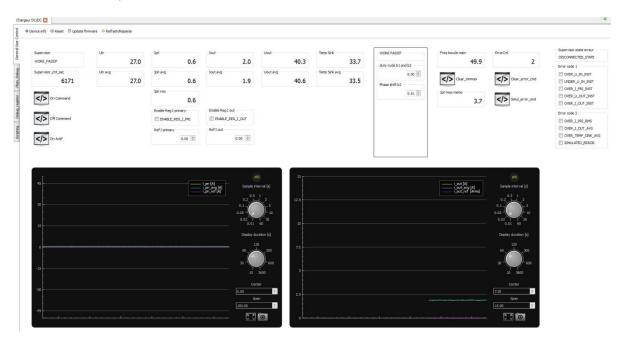

|    | 6.4   | Codage et régulation                    | 77 |

|    | 6.4.1 | 1 Codage du CPLD                        | 77 |

|    | 6.4.2 | 2 Codage du DSP                         | 78 |

|    | 6.5   | Synthèse de la phase d'intégration      | 83 |

| 7  | Phas  | se 5 : Vérification                     | 84 |

|    | 7.1   | Protocole de vérification des PCBs      | 84 |

|    | 7.2   | Méthode de test                         | 85 |

|    | 7.3   | Protocole de contrôle de fonctionnement | 85 |

|    | 7.4   | Tests et mesures                        | 86 |

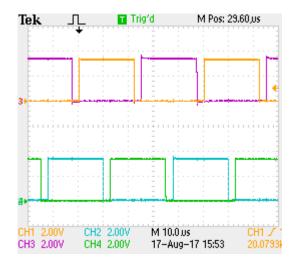

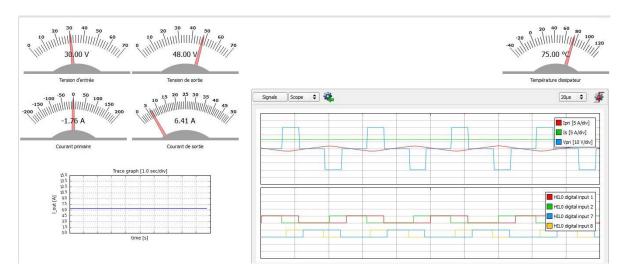

|    | 7.4.1 | 1 Formes d'ondes                        | 87 |

|    | 7.4.2 | 2 Rendement                             | 90 |

|    | 7.4.3 | 3 Améliorations                         | 91 |

|    | 7.5   | Synthèse de la phase de vérification    | 91 |

| 8  | Conc  | clusion                                 | 92 |

| 9  | Signa | nature                                  | 92 |

| 10 | Ві    | Bibliographie                           | 93 |

| 11 | Aı    | Annexes                                 | 93 |

#### 1 Introduction

Ce projet traite de la réalisation d'un convertisseur DC/DC en partant du choix de la topologie et de simulations du comportement du système jusqu'à la construction de celui-ci, en passant par l'implémentation d'une structure de réglage propre au dispositif.

Ce convertisseur a pour vocation de s'intégrer dans un système plus vaste permettant de fournir l'énergie nécessaire à un dispositif d'imagerie médicale de type radiographie.

La particularité de ce convertisseur est sa plage de tension d'entrée pouvant varier de 24 à 48[VDC].

#### 2 Cahier des charges

#### 2.1 Introduction

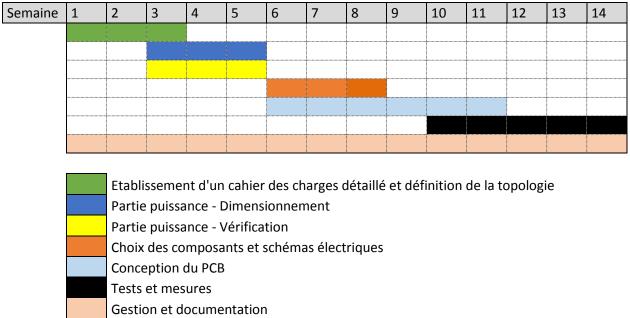

Le présent cahier des charges se concentre sur le chargeur DC/DC pour l'interfaçage d'une source d'énergie (batterie, panneaux photovoltaïques) avec le bus continu du système, soit la batterie de stockage intermédiaire.

#### 2.2 Description

Dans le cadre d'une collaboration avec un partenaire industriel, le Laboratoire d'Electronique Industrielle (EoI) est en charge de réaliser un dispositif d'alimentation afin de connecter un système d'imagerie médicale (Radiographie) à un réseau électrique monophasé basse tension. Le but est de garantir la fonctionnalité et l'autonomie du système grâce à des éléments d'accumulation d'énergie et cela indépendamment de l'état du réseau (même en l'absence de tension réseau pour une durée déterminée).

Un bus batterie (DC) intermédiaire permet de découpler le réseau du système d'imagerie médicale. Afin de charger la batterie connectée au bus, deux chargeurs sont utilisés : le premier permet la recharge de la batterie grâce au réseau (AC/DC) et le second (DC/DC) doit être réalisé afin de permettre l'utilisation d'une autre source d'énergie de type continue. Ce projet se concentre sur le deuxième type de convertisseur (DC/DC).

Les sources d'énergie sont principalement de trois types différents :

- Bus continu (DC) d'une installation photovoltaïque

- Installation photovoltaïque directe

- Batterie auxiliaire

La commande ainsi que la régulation du chargeur sont réalisées grâce à un processeur de signal numérique (DSP – Digital Signal Processor) qui contrôle le système de manière globale. Le chargement de la batterie sur le bus continu peut être effectué par le chargeur AC/DC et/ou par le chargeur DC/DC. Un algorithme de contrôle du système complet (chargeur AC/DC et DC/DC) doit permettre de contrôler les deux convertisseurs mais ne fait pas l'objet de ce projet.

Carreto Romain 3 / 93

#### 2.3 Objectifs

Les objectifs principaux de ce projet sont :

- Analyse de spécifications et dimensionnement d'un dispositif.

- Mise en œuvre et tests sur le module dimensionné.

- Remise d'un dossier technique complet et documentation.

Plus particulièrement, le module de conversion à développer comportera trois étapes principales :

- Analyse du sous-système à développer. Définition et analyse des spécifications relatives au module à développer.

- Mise en œuvre des procédures et outils de dimensionnement du sous-système. Dimensionnement et simulations de pré-validation.

- Prototypage du dispositif et tests si le temps imparti est suffisant.

#### 2.4 Schéma fonctionnel

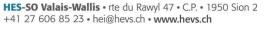

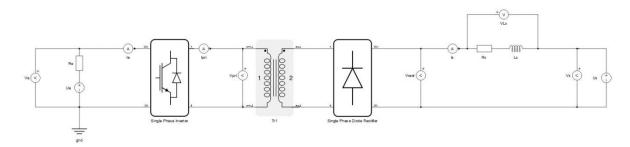

Ci-dessous (Figure 1), le schéma de principe de l'installation complète :

Figure 1 : Schéma fonctionnel simplifié de l'installation

Le projet se concentre sur le convertisseur DC/DC encadré en rouge sur la Figure 1. Les parties à réaliser sont : partie puissance du dispositif, prise de mesures (capteurs de courant et tension), commande des interrupteurs par des drivers, interfaçage des mesures et commandes avec la carte DSP et codage de la régulation dans le DSP.

#### 2.5 Spécifications et contraintes

Les spécifications concernant le chargeur DC/DC sont :

- Plage de tension de la source d'énergie : 12..48[V] (La plage pouvant être réduite à 24..48[V] si la première est trop ambitieuse).

- Sources de type différentes : Bus continu de panneaux PVs, panneaux PVs en liaison directe, batterie auxiliaire.

- Tension du bus continu : 48[V].

- Capacité de la batterie sur le bus continu : 20[Ah].

Carreto Romain 4 / 93

- Type de charge : rapide ( $Icharge = \frac{C}{2.5} = 8[A]$  soit 3[h] de chargement), lente ( $Icharge = \frac{C}{10} = 2[A]$  soit 10[h] de chargement).

- Type de batterie : NiMH Nickel-Hydrure métallique.

- Puissance pouvant transiter dans le chargeur : 500[W] maximum.

#### Les contraintes à respecter sont les suivantes :

- Topologie abaisseur/élévateur.

- Convertisseur monodirectionnel.

- Séparation galvanique par le biais d'un transformateur travaillant à haute fréquence pour la diminution de volume.

- Optimisation du chargement de la batterie sur le bus continu au détriment du MPPT de la source d'énergie : si la puissance demandée par la batterie est plus grande que la puissance maximale disponible par les panneaux solaires, le MPPT est réalisé sinon la puissance prélevée sera diminuée afin de respecter l'optimisation du chargement de la batterie (ce point ne sera pas implémenté dans ce projet.).

- Gestion de la commande et régulation par un organe central (DSP).

- Sécurité software pour l'enclenchement et le déclenchement du chargeur (contrôlé par le DSP).

#### 2.6 Tâches à réaliser

Voici les tâches principales devant être réalisées :

- Définition de la topologie du chargeur DC/DC :

- Définir une stratégie pour réduire le coût du convertisseur (topologie minimale nécessaire), obtenir un rendement maximal et charger la batterie de manière optimale (contrôle du courant de charge).

- Choix de la topologie selon les critères à respecter (cf. Spécifications et contraintes).

- Dimensionnement de la partie puissance :

- o A l'aide d'un logiciel de simulation (« Simplorer ») :

- Mise en équations du sous-système.

- Calcul des valeurs d'inductances, condensateurs et du transformateur (contrôle à l'aide de simulations).

- Stratégie de commande et de régulation (tension et courant de sortie, contrôle de la puissance prélevée).

- Machine d'état pour les mises sous/hors tension ainsi que les modes de fonctionnement (via le DSP).

- Choix des fréquences de commutations.

- Calcul des valeurs de tension et courants sur les éléments (contrôle à l'aide de simulations).

- o A l'aide d'un logiciel de simulation en temps réel (« Typhoon HIL ») :

- Contrôle du fonctionnement du code (DSP), formes d'ondes.

- Choix des composants et conception du/des PCBs :

- Recherche de composants répondants aux critères définis dans les tâches précédentes.

Carreto Romain 5 / 93

- Calcul des pertes pour identifier le rendement (et simulations pour le contrôle des calculs): dans un premier temps avec les valeurs de composants usuels (approximation) puis avec les valeurs des composants commandés.

- Schémas électriques

- o Conception du/des PBCs à l'aide d'un logiciel de routage (« Altium Designer »).

- o Dimensionnement du dissipateur thermique et contrôle de sa température.

#### • Tests et mesures :

- Etablissement d'un protocole de test afin de vérifier le bon fonctionnement du dispositif.

- Mesures sur un banc d'essai si le temps le permet.

#### 2.7 Planning prévisionnel

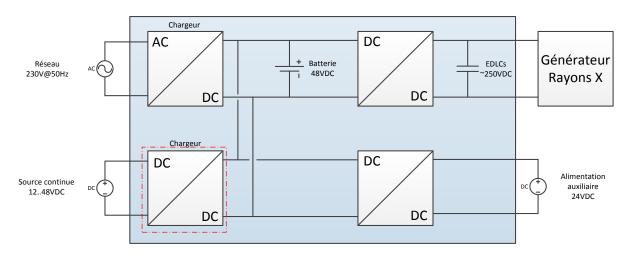

Le planning ci-dessous (Tableau 1) regroupe les principales tâches à réaliser au cours du projet :

Tableau 1 : Planning prévisionnel

#### 2.8 Remarques

Ce cahier des charges regroupe toutes les informations disponibles à ce jour (18.05.17). Il reste des spécifications à définir durant l'avancement du projet.

Carreto Romain 6 / 93

#### 3 Phase 1: Spécification

Cette phase définit la structure du convertisseur à réaliser pour la fonction demandée à partir de considérations logiques et pratiques.

#### 3.1 Choix de la topologie

Afin de définir la topologie la mieux adaptée au cahier des charge, une multitude de possibilités peuvent être envisagées.

La convention pour les schémas ci-dessous respecte la figure suivante (Figure 2) :

Figure 2 : Convention pour les topologies de convertisseurs

Les topologies présentées ci-dessous prennent en compte les niveaux de tension à respecter. Les convertisseurs sans séparation galvanique sont également pris en considération.

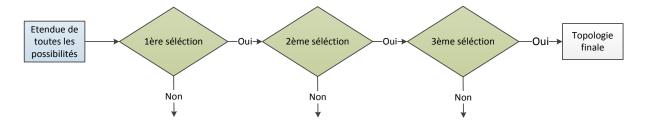

Pour garantir la topologie la plus propice à l'application, une sélection par étape est réalisée. Le choix peut être représenté de la manière suivante :

Figure 3 : Processus de sélection

Une première sélection écarte toutes les topologies ne répondant pas au cahier des charges ou ayant des caractéristiques supérieures à celles attendues. Une seconde sélection, plus précise, permet de sélectionner la topologie la plus efficace pour l'application demandée (fonction). Enfin, la troisième sélection détermine et compare les différentes structures ayant la même fonction.

En tout, 24 structures différentes sont considérées : Buck, Boost, Buck-Boost, 2-Quadrants, SEPIC (avec/sans séparation galvanique), résonant, Forward, Push-Pull, Flyback, CUK, 4-Quadrants (13 variantes) (avec/sans séparation galvanique).

Afin de ne pas surcharger le rapport, tous les schémas de structures se trouvent sous l'annexe 1. Seules les structures passant la première sélection seront décrites dans ce rapport.

Carreto Romain 7 / 93

#### 3.2 Première sélection

Le premier critère du cahier des charges qui permet de retirer une grande partie des convertisseurs est la séparation galvanique. Les topologies **Buck**, **Boost**, **Buck-Boost**, **2-Quadrants**, **SEPIC** (sans séparation galvanique), **résonant**, **CUK** et **4-Quadrants Full- ou Half-Bridge** sans séparation galvanique (2 variantes) peuvent être exclues. Ces structures ne sont soit pas prévues pour recevoir un transformateur (ou n'en n'ont pas), soit asymétriques en tension et donc à risque de saturation sur le transformateur. Les structures **Buck** et **Boost** ne répondent également pas au critère « élévateur et abaisseur de tension » du cahier des charges.

Ensuite, une topologie monodirectionnelle suffit. Il serait inutile de considérer la bidirectionnalité car elle fonctionnerait mais élèverait le coût du dispositif. Les variantes **4-Quadrants** réversibles en courant et/ou tension sont ainsi écartées du choix.

Cette première sélection réduit donc le choix aux convertisseurs suivants : **SEPIC**, **Forward**, **Push-Pull**, **Flyback**, **4-Quadrants** (6 variantes). Tous disposent d'une séparation galvanique.

#### 3.3 Deuxième sélection

Cette sélection traite de la saturation des transformateurs, des contraintes en tension et/ou courant sur les différents éléments, des degrés de liberté pour la régulation ainsi que des formes d'ondes pour établir le choix de la topologie.

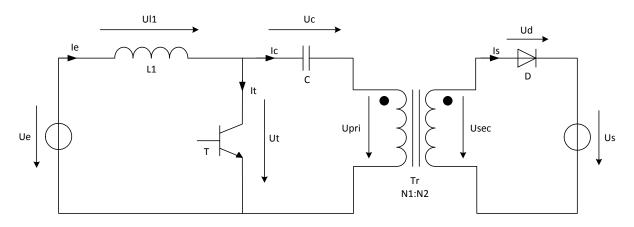

#### Topologie SEPIC :

Figure 4 : Convertisseur SEPIC avec isolation galvanique

Tout d'abord, la topologie du SEPIC avec séparation galvanique n'est pas retenue pour des raisons de régulation difficile à implémenter.

De plus, le courant circulant dans le primaire du transformateur est de valeur moyenne non nulle obligeant à surdimensionner le transformateur pour éviter une saturation magnétique. Ce sont pour ces différentes raisons que la topologie du SEPIC n'a pas été prise en compte.

Carreto Romain 8 / 93

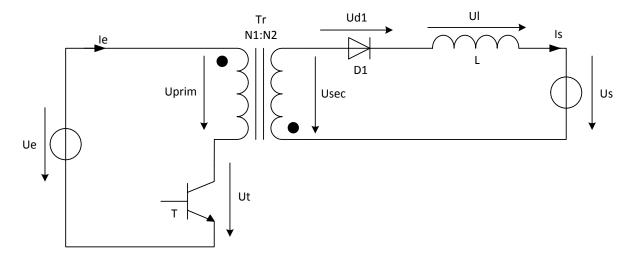

#### > Topologie Flyback :

Figure 5 : Convertisseur Flyback

Tout d'abord, le courant magnétisant ne peut que circuler dans un sens, l'interrupteur T étant unidirectionnel en courant. Le transformateur doit alors être surdimensionné afin d'éviter de saturer magnétiquement (courant moyen non nul).

De plus, l'inductance magnétisante à choisir pour le dimensionnement du transformateur dépend fortement de la tension d'entrée ( $U_{in}^2$  proportionnel à  $L_p$ ). Sachant que la tension d'entrée peut varier entre 12..48[V] (soit d'un rapport 4), le transformateur ne sera donc pas optimal pour chaque point de fonctionnement.

#### ➤ Topologie Forward :

Figure 6 : Convertisseur Forward

Le facteur principal qui a écarté cette topologie est le courant magnétisant unipolaire circulant dans le transformateur. Comme pour la topologie **Flyback**, le transformateur doit être surdimensionné pour éviter la saturation magnétique (courant moyen non nul).

Carreto Romain 9 / 93

#### Topologie Push-Pull:

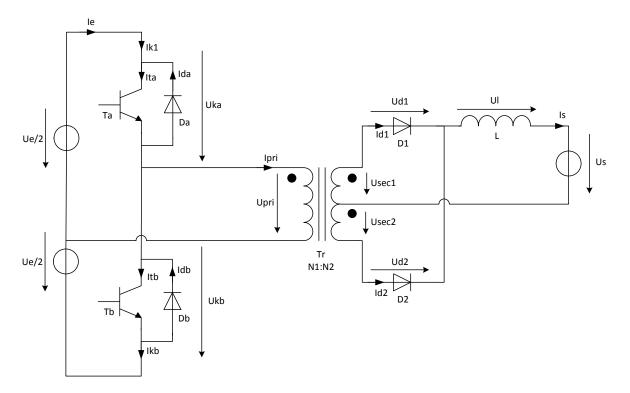

Figure 7: Convertisseur Push-Pull

Les deux alimentations de tension de valeur  $\frac{U_e}{2}$  n'existent pas directement sur l'installation, la source doit être considérée comme une source unique de tension. Il est alors possible de remplacer ces deux alimentations par des condensateurs afin d'obtenir un diviseur de tension capacitif. Cette topologie revient alors à celle d'un 4-Quadrants en demi-pont (deux condensateurs et deux cellules de commutations). Cette topologie est considérée dans le chapitre suivant « Synthèse et décision ».

Les topologies ci-dessus ont souvent l'inconvénient de magnétiser le transformateur de manière asymétrique entrainant de ce fait un surdimensionnement. Les convertisseurs restants proposent un courant moyen nul dans le transformateur.

Les topologies ci-dessus n'étant pas optimales pour l'application désirée, il reste les topologies de type **4-Quadrants** (8 variantes) à traiter.

Carreto Romain 10 / 93

#### 3.4 Synthèse et décision sur la topologie

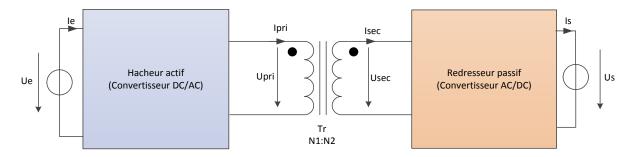

La topologie globale du système est représentée sur la figure suivante (Figure 8) :

Figure 8 : Schéma de la topologie finale

Il s'agit d'un convertisseur de type « DC/AC/DC ».

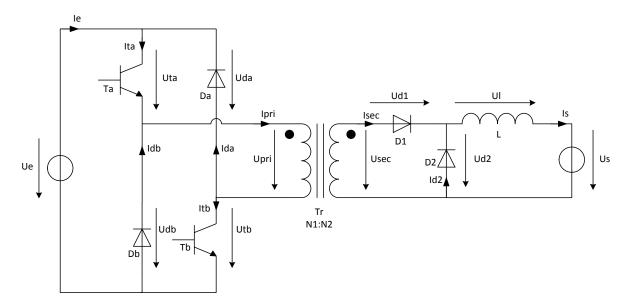

Dans le bloc « Hacheur actif » de la Figure 8, deux configurations sont possibles :

Figure 9 : Types d'hacheurs actifs, Half-Bridge (à gauche) et Full-Bridge (à droite)

Parmi ces deux solutions, la solution « Full-Bridge » (Figure 9 à droite) est retenue pour plusieurs facteurs.

La tension de sortie du pont complet peut atteindre la tension d'alimentation par rapport au demipont qui est limité à la moitié de la tension d'alimentation (point milieu de tension fixe entre les 2 condensateurs). A puissance égale, le courant circulant dans le transformateur sera donc plus grand avec le demi-pont qu'avec le pont complet. Les pertes par effet Joule seront plus élevées pour la configuration demi-pont.

De plus, le système Half-Bridge est également limité par les courants maximaux admissibles par les condensateurs (risque d'échauffement, robustesse du dispositif réduite).

Carreto Romain 11 / 93

Le choix d'un pont complet rajoute certes des drivers à acheter pour la commande du deuxième bras. Cependant, la commande du demi-pont doit entrainer une attention particulière à l'équilibrage des tensions sur les condensateurs afin d'éviter des asymétries en tension. C'est pourquoi le pont complet est retenu pour le convertisseur à réaliser.

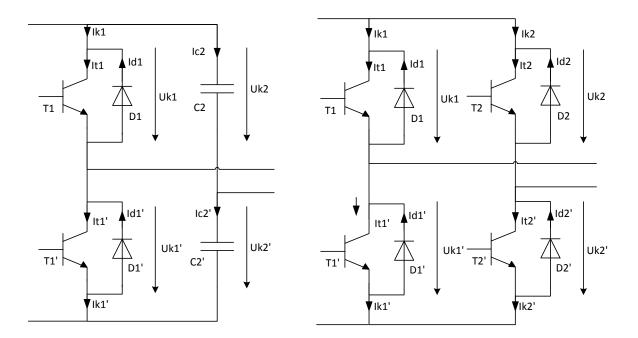

Pour le bloc « Redresseur passif » de la Figure 8, 4 configurations sont possibles :

Figure 10 : De haut en bas et de gauche à droite : Redresseur simple-alternance, Redresseur du convertisseur Forward, Redresseur double-alternances à point milieu et redresseur en pont de Graetz

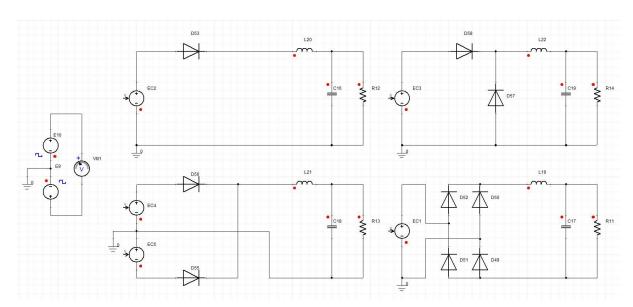

Une simulation a permis de comparer les 4 types de redresseurs. Les schémas de simulation sont les suivants :

Figure 11: Simulation des redresseurs

La source de tension en sortie est remplacée par une résistance en parallèle d'un condensateur de lissage. Les valeurs d'inductance et de condensateurs sont identiques pour chaque redresseur.

Carreto Romain 12 / 93

La puissance consommée par chaque redresseur est également identique :

$$L = 100[nH], C = 100[\mu F], P = 250[W]$$

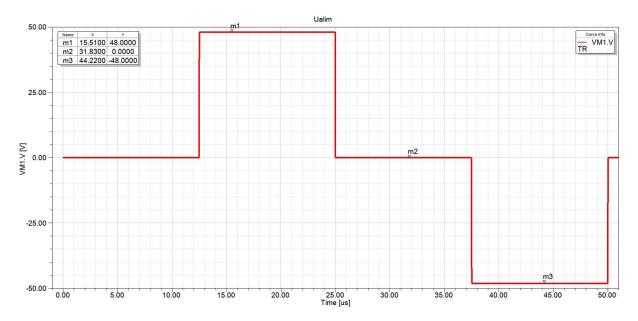

Le secondaire du transformateur est modélisé par une source de tension rectangulaire d'amplitude 48[V] et de fréquence 20[kHz] :

Figure 12 : Allure de la tension d'alimentation des redresseurs

Il s'agit de la somme de deux signaux carré déphasés de  $90^\circ$  créant ce signal avec des passages par zéro de tension.

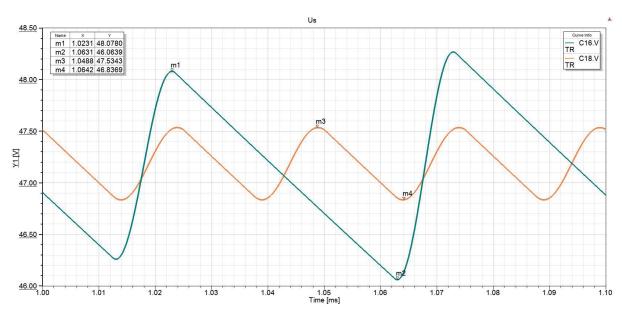

Les tensions sur les charges sont les suivantes :

Figure 13: Tensions en sortie des redresseurs

La courbe rouge sur la Figure 13 représente l'allure de la tension de sortie des redresseurs simplealternance ; la courbe bleue, l'allure de la tension de sortie des redresseurs double-alternances.

Carreto Romain 13 / 93

Les résultats montrent des oscillations doubles en courant et tension pour les deux redresseurs du haut de la Figure 10. Ceci s'explique par le fait qu'il s'agit d'un redressement simple-alternance. Pour avoir les mêmes ondulations en tension, le condensateur doit avoir une capacité double.

Pour les deux redresseurs double-alternances (bas de la Figure 10), leur comportement est similaire. La fréquence vue par la charge est double par rapport à la fréquence de la tension d'alimentation.

Le pont de Graetz devance le redresseur à point milieu : l'ajout de deux diodes par rapport à la suppression du point milieu du secondaire du transformateur reste moins coûteux sachant que des ponts de diodes peuvent s'acheter en module prêt à l'emploi.

De plus, la construction du transformateur reste compliquée car elle doit garantir un couplage uniforme entre les différents enroulements pour garantir la symétrie en tension ainsi que des inductances de fuites minimales et de valeurs semblables pour chaque enroulement.

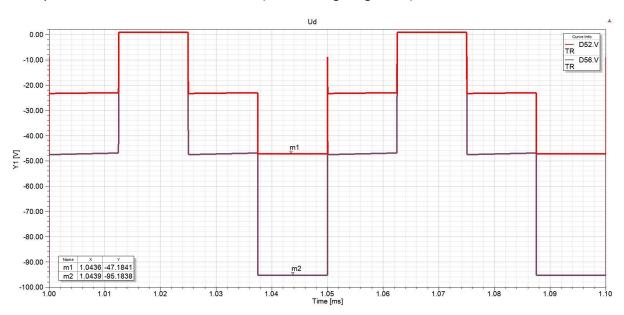

Enfin, la configuration du redressement avec point milieu impose des contraintes en tension plus importantes sur les diodes lorsqu'elles sont bloquées. En effet, la tension inverse sur les diodes vaut deux fois la tension d'alimentation (Courbe verte, Figure 14) alors que pour le pont de Graetz elle ne vaut qu'une fois la tension d'alimentation (Courbe rouge, Figure 14) :

Figure 14: Contraintes en tension sur les diodes (PIV)

#### Remarque:

Afin d'obtenir la même puissance consommée pour chaque topologie de redresseur, la résistance de charge a été adapté dans chaque cas.

Carreto Romain 14 / 93

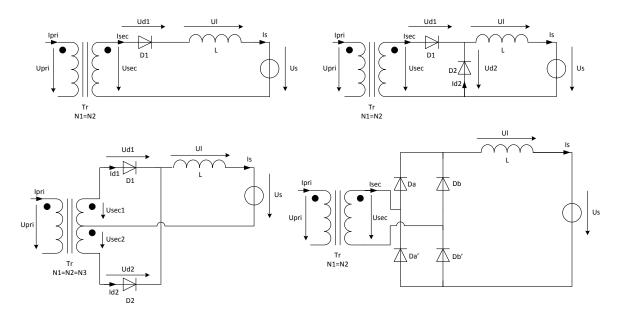

La topologie finale qui est alors sélectionnée est la suivante :

Figure 15 : Topologie choisie

Il s'agit bien évidement du schéma de base qui peut être sujet à des modifications par la suite.

Carreto Romain 15 / 93

#### 4 Phase 2 : Conception

Cette section a pour but d'établir le fonctionnement du dispositif de manière parfaitement clair et précise. Une étude systématique est réalisée afin de comprendre les relations de cause à effet qui régissent le comportement du chargeur.

Un fois cette démarche réalisée, il est possible de définir les types de flux dans les différentes parties du circuit et donc de dimensionner les éléments principaux tels qu'inductances, condensateurs et transformateur. Les valeurs maximales sur les composants peuvent également être définies.

Enfin, la régulation peut être implémentée en inversant les relations de cause à effet précédemment définies.

Cette phase s'inspire du livre «°Pulse-Width Modulated DC-DC Power Converters°» (Référence [1]).

#### 4.1 Système en boucle ouverte

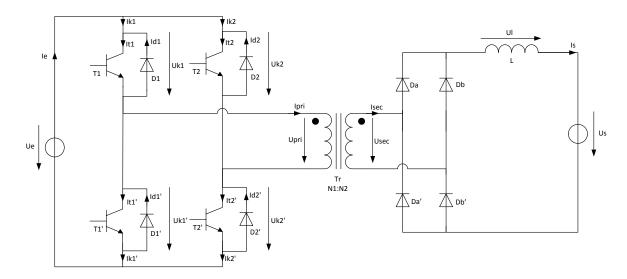

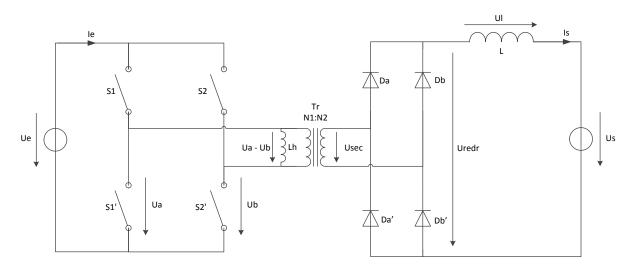

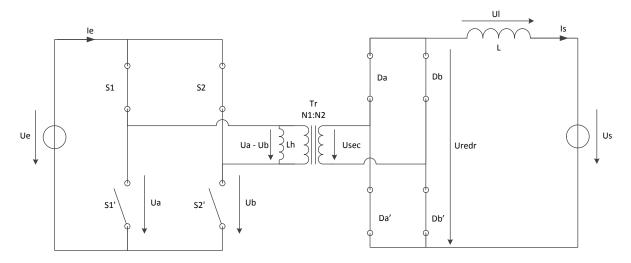

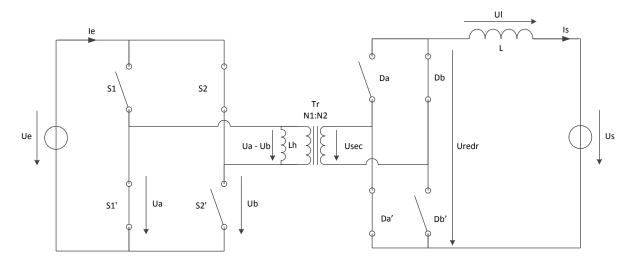

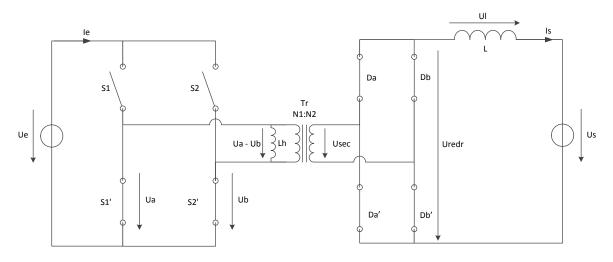

La commande du système agit sur l'ouverture et la fermeture des semi-conducteurs. Ceux-ci peuvent être modélisés par des interrupteurs comme sur la figure suivante (Figure 16) :

Figure 16 : Schéma de principe de la commande des interrupteurs

La tension d'alimentation est représentée par la variable  $U_e$ , la tension de point milieu de chaque bras par les variables respectives  $U_a$  et  $U_b$ . La tension au primaire du transformateur vaut donc  $U_a-U_b$ .

La commande de chaque bras est indépendante. Le rapport cyclique de chaque bras est de D=50%.

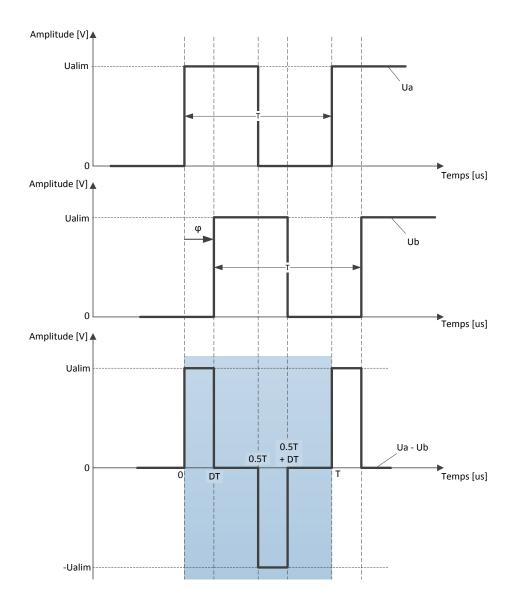

Afin de varier la tension moyenne en sortie du redresseur, un déphasage  $\varphi$  est inséré entre la commande de chaque bras :

Carreto Romain 16 / 93

Figure 17 : Graphe temporel de la commande du pont en H

La Figure 17 montre l'allure de la tension appliquée au primaire du transformateur. Une fois redressée, cette tension possèdera une valeur moyenne dépendante du déphasage de la commande entre les deux bras du pont en H. La relation entre le rapport cyclique et le déphasage est :

$$D = \frac{\varphi}{2 \cdot \pi} \ avec \ \varphi \in [0; \pi]$$

Il est important de noter que ce rapport cyclique n'a rien à voir avec le rapport cyclique de chaque bras du pont en H qui seront notés  $d_1$  et  $d_2$ . La conversion du déphasage ci-dessus sert uniquement à normaliser le déphasage entre 0 et 1 (pour un déphasage compris entre 0 et 1 et 10 et 11 (pour un déphasage compris entre 12 et 13 et 13 et 14 et 15 et 15 et 15 et 15 et 16 et 16 et 17 et 16 et 17 et 17 et 18 et 19 et

L'étude complète pour chaque phase de la tension appliquée au primaire du transformateur est réalisée dans la section suivante.

#### 4.1.1 Equations liés à la topologie

L'analyse se réfère à la topologie de la Figure 16. Chaque intervalle de temps correspond au graphe temporel de la Figure 17. Les hypothèses à considérer sont les suivantes :

Carreto Romain 17 / 93

- Les interrupteurs sont considérés comme idéaux (pas de chute de tension, pas de pertes).

- Le transformateur est représenté par son inductance de magnétisation et un rapport de transformation uniquement.

- Les sources de tension sont idéales (pas de résistance interne).

- Les éléments passifs sont considérés comme linéaires et indépendants de la fréquence.

- L'analyse se fait lors du régime établi, en conduction continue.

L'analyse ci-dessous est réalisée en conduction continue car ce mode de fonctionnement est avantageux. La raison d'un fonctionnement discontinu est le sous dimensionnement des éléments tel qu'inductances et transformateurs lorsque la topologie est plutôt de type « Flyback », c'est-à-dire que le transformateur sert de réservoir intermédiaire d'énergie et donc que son inductance magnétisante doit être de valeur faible. La topologie choisie est plutôt de type « Forward » (sans stockage intermédiaire d'énergie). Le transformateur sert uniquement à l'élévation de la tension et à la séparation galvanique. La valeur de l'inductance magnétisante peut alors être grande. Un mode de fonctionnement en conduction continu convient alors parfaitement.

La fréquence de commutation est définie comme suit :  $f_{com} = \frac{1}{r}$ .

L'analyse comprend 4 configurations des interrupteurs. Les temps morts afin d'éviter les courtscircuits ne sont pas pris en considération dans l'analyse. Des diodes seront montées en antiparallèle des interrupteurs  $S_1$ ,  $S_1'$ ,  $S_2$  et  $S_2'$  afin de garantir la conduction lors des temps mort. Si les interrupteurs sont de type MOSFET, ils pourront conduire le courant dans les deux sens.

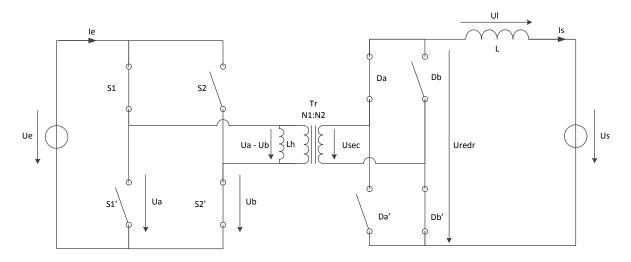

#### 1. Intervalle $0 < D \cdot T$ :

Les interrupteurs et diodes qui conduisent sont  $S_1$ ,  $S_2'$ ,  $D_a$  et  $D_b'$ .

Figure 18 : Configuration des interrupteurs pour l'intervalle de temps  $0 < D \cdot T \,$

Tension en fonction du temps aux bornes de l'inductance de magnétisation  $L_h$ :

$$U_{L_h} = U_e = L_h \cdot \frac{dI_{L_h}}{dt}$$

Carreto Romain 18 / 93

Courant en fonction du temps aux bornes de l'inductance de magnétisation  $L_h$ :

$$I_{L_h}(t) = \frac{1}{L_h} \cdot \int_0^t U_{L_h}(t) \cdot dt + I_{L_h}(0) = \frac{U_e \cdot t}{L_h} + I_{L_h}(0)$$

Ondulations de courant sur l'inductance de magnétisation  $L_h$ :

$$\Delta I_{L_h} = I_{L_h}(D \cdot T) - I_{L_h}(0) = \frac{U_e \cdot D \cdot T}{L_h} = \frac{U_e \cdot D}{L_h \cdot f_{com}}$$

Sachant que les ondulations de courant sont symétriques autour de 0[A]:

Si t = 0:

$$I_{L_h}(0) = -\frac{U_e \cdot D}{2 \cdot L_h \cdot f_{com}}$$

Si  $t = D \cdot T$ :

$$I_{L_h}(D \cdot T) = + \frac{U_e \cdot D}{2 \cdot L_h \cdot f_{com}}$$

La valeur de l'inductance de magnétisation minimale  $L_{h,min}$  du transformateur peut alors être définie :

$$L_{h,min} = \frac{U_{e,max} \cdot D_{min}}{\Delta I_{L_h,max} \cdot f_{com}}$$

Tension aux bornes de l'inductance de sortie L:

$$U_L = U_{redr} - U_s = \frac{U_h}{n} - U_s = \frac{U_e}{n} - U_s = L \cdot \frac{dI_L}{dt}$$

Courant en fonction du temps dans l'inductance de sortie L:

$$I_{S}(t) = I_{L}(t) = \frac{1}{L} \cdot \int_{0}^{t} U_{L} \cdot dt = \frac{1}{L} \cdot \int_{0}^{t} (U_{redr} - U_{S}) \cdot dt = \frac{1}{L} \cdot \int_{0}^{t} \left(\frac{U_{e}}{n} - U_{S}\right) \cdot dt$$

$$= \frac{1}{L} \cdot \left(\frac{U_{e}}{n} - U_{S}\right) \cdot t + I_{L}(0)$$

Ondulations de courant sur l'inductance de sortie L:

$$\Delta I_L = I_L(D \cdot T) - I_L(0) = \frac{1}{L} \cdot \left(\frac{U_e}{n} - U_s\right) \cdot D \cdot T = \frac{1}{L \cdot f_{com}} \cdot \left(\frac{U_e}{n} - U_s\right) \cdot D$$

Sachant que les ondulations de courant sont symétriques autour de  $I_{L,moy}$ :

Si t = 0:

$$I_L(0) = I_{L,moy} - \frac{1}{2} \cdot \Delta I_L = I_{L,moy} - \frac{1}{2 \cdot L \cdot f_{com}} \cdot \left(\frac{U_e}{n} - U_s\right) \cdot D$$

Carreto Romain 19 / 93

20 / 93

Si  $t = D \cdot T$ :

$$I_L(D \cdot T) = I_{L,moy} + \frac{1}{2} \cdot \Delta I_L = I_{L,moy} + \frac{1}{2 \cdot L \cdot f_{com}} \cdot \left(\frac{U_e}{n} - U_s\right) \cdot D$$

Sachant que la tension moyenne de sortie  $U_s$  vaut :

$$U_s = 2 \cdot D \cdot U_{redr} = 2 \cdot D \cdot \frac{U_e}{n} \Leftrightarrow \frac{U_e}{n} = \frac{U_s}{2 \cdot D}$$

Les ondulations de courant sur l'inductance L peuvent alors s'écrire de la manière suivante :

$$\Delta I_L = \frac{U_S}{L \cdot f_{com}} \cdot \left(\frac{1}{2} - D\right)$$

Les ondulations maximales de courant en sortie valent :

$$\Delta I_{L,max} = \frac{U_s}{L \cdot f_{com}} \cdot \left(\frac{1}{2} - D_{min}\right)$$

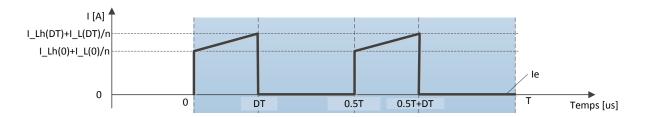

Courant en fonction du temps donné par la source :

$$\begin{split} I_{e}(t) &= I_{L_{h}}(t) + \frac{I_{L}(t)}{n} = \frac{U_{e} \cdot t}{L_{h}} + I_{L_{h}}(0) + \frac{1}{L \cdot n} \cdot \left(\frac{U_{e}}{n} - U_{s}\right) \cdot t + \frac{I_{L}(0)}{n} \\ &= \left(U_{e} \cdot \left(\frac{1}{n^{2} \cdot L} + \frac{1}{L_{h}}\right) - \frac{U_{s}}{L \cdot n}\right) \cdot t + I_{L_{h}}(0) + \frac{I_{L}(0)}{n} \end{split}$$

Si t = 0:

$$I_e(0) = I_{L_h}(0) + \frac{I_L(0)}{n}$$

Si  $t = D \cdot T$ :

$$I_e(D \cdot T) = \left(U_e \cdot \left(\frac{1}{n^2 \cdot L} + \frac{1}{L_h}\right) - \frac{U_s}{L \cdot n}\right) \cdot D \cdot T + I_{L_h}(0) + \frac{I_L(0)}{n}$$

Les contraintes sur les interrupteurs sont :

$$U_{int.max} = U_e$$

$$I_{int,max} = I_{L_h}(D \cdot T) + \frac{I_L(D \cdot T)}{n} = \frac{U_e \cdot D}{2 \cdot L_h \cdot f_{com}} + \frac{U_s}{2 \cdot L \cdot f_{com} \cdot n} \cdot \left(\frac{1}{2} - D\right) + \frac{I_{L,moy}}{n}$$

Les contraintes sur les diodes du redresseur sont :

$$U_{d,redr,max} = \frac{U_e}{n}$$

$$I_{d,redr,max} = I_L(D \cdot T) = \frac{U_S}{2 \cdot L \cdot f_{com}} \cdot \left(\frac{1}{2} - D\right) + I_{L,moy}$$

Carreto Romain

#### 2. Intervalle $D \cdot T < 0.5 \cdot T$ :

Les interrupteurs et diodes qui conduisent sont  $S_1$ ,  $S_2$ ,  $D_a$  et  $D_b'$ .

Figure 19 : Configuration des interrupteurs pour l'intervalle de temps D·T  $< 0.5 \cdot T$

Tension en fonction du temps aux bornes de l'inductance de magnétisation  $\mathcal{L}_h$  :

$$U_{L_h} = 0 = L_h \cdot \frac{dI_{L_h}}{dt}$$

Courant en fonction du temps aux bornes de l'inductance de magnétisation  $\mathcal{L}_h$ :

$$I_{L_h}(t) = I_{L_h}(D \cdot T) = \frac{U_e \cdot D}{2 \cdot L_h \cdot f_{com}}$$

Tension aux bornes de l'inductance de sortie L:

$$U_L = -U_S = L \cdot \frac{dI_L}{dt}$$

Courant en fonction du temps dans l'inductance de sortie L:

$$I_S(t) = I_L(t) = \frac{1}{L} \cdot \int_{D \cdot T}^t U_L \cdot dt = \frac{1}{L} \cdot \int_{D \cdot T}^t (-U_S) \cdot dt = -\frac{U_S}{L} \cdot (t - D \cdot T) + I_L(D \cdot T)$$

Ondulations de courant sur l'inductance de sortie L:

$$\Delta I_L = I_L \left( \frac{1}{2} \cdot T \right) - I_L (D \cdot T) = -\frac{U_S}{L} \cdot \left( \frac{1}{2} \cdot T - D \cdot T \right) = -\frac{U_S}{L \cdot f_{com}} \cdot \left( \frac{1}{2} - D \right)$$

Les ondulations maximales de courant en sortie valent :

$$\Delta I_{L,max} = -\frac{U_s}{L \cdot f_{com}} \cdot \left(\frac{1}{2} - D_{min}\right)$$

Carreto Romain 21 / 93

#### 3. Intervalle $0.5 \cdot T < 0.5 \cdot T + D \cdot T$ :

L'analyse est similaire à l'intervalle de temps 1. Les interrupteurs et diodes qui conduisent sont  $S'_1$ ,  $S_2$ ,  $D'_a$  et  $D_b$ .

Figure 20 : Configuration des interrupteurs pour l'intervalle de temps  $0.5 \cdot T < 0.5 \cdot T + D \cdot T$

#### 4. Intervalle $0.5 \cdot T + D \cdot T < T$ :

L'analyse est similaire à l'intervalle de temps 2. Les interrupteurs et diodes qui conduisent sont  $S_1'$ ,  $S_2'$ .

Figure 21 : Configuration des interrupteurs pour l'intervalle de temps  $0.5 \cdot T + D \cdot T < T$

Carreto Romain 22 / 93

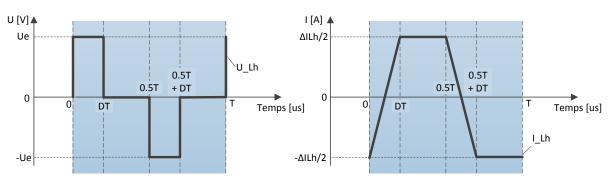

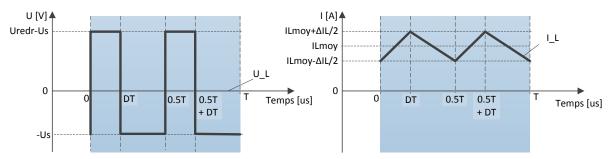

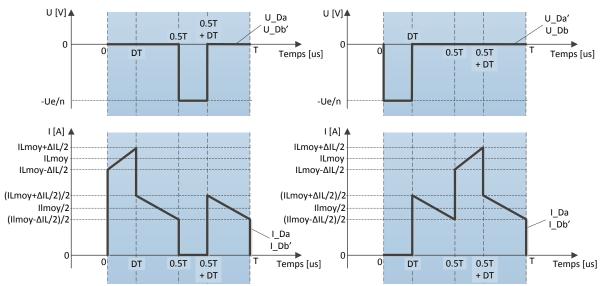

#### 4.1.2 Formes d'ondes

Les formes des courants et tension sont représentées dans les schémas suivants.

Figure 22 : Courant pris à la source

Figure 23 : Tension et courant sur l'inductance de magnétisation du transformateur

Figure 24 : Tension et courant sur l'inductance de sortie

Carreto Romain 23 / 93

Figure 25: Tensions et courants sur les interrupteurs

Figure 26: Tensions et courants sur les diodes du redresseur

#### 4.1.3 Dimensionnement des éléments principaux

Il faut dans un premier temps définir quelques relations générales. Le rendement du dispositif est considéré unitaire. Les graphes présentés ci-dessous découlent de calculs disponibles sous « Annexe 2 : Scripts Matlab ».

Carreto Romain 24 / 93

25/93

Courant d'entrée moyen :

$$< I_e > = \frac{1}{T} \cdot \int_0^T I_e(t) \cdot dt = \frac{2}{T} \cdot \int_0^{D \cdot T} I_e(t) \cdot dt = \frac{2}{T} \cdot \int_0^{D \cdot T} \left( \frac{I_e(D \cdot T) - I_e(0)}{D \cdot T} \cdot t + I_e(0) \right) \cdot dt$$

$$= \frac{2}{T} \cdot \left[ \frac{I_e(D \cdot T) - I_e(0)}{D \cdot T} \cdot \frac{t^2}{2} + I_e(0) \cdot t \right]_0^{D \cdot T} = D \cdot \left( I_e(0) + I_e(D \cdot T) \right)$$

Courant de sortie moyen :

$$\langle I_{S} \rangle = \langle I_{L} \rangle = \frac{U_{S}}{R_{load}}$$

Puissance de sortie moyenne :

$$P_S = \langle U_S \rangle \langle I_S \rangle$$

Impédance de sortie :

$$Z_S = \frac{\langle U_S \rangle}{\langle I_S \rangle}$$

Rapport de transformation :

$$n = \frac{N_1}{N_2} = \frac{\langle U_1 \rangle}{\langle U_2 \rangle} = \frac{\langle U_e \rangle}{\langle U_{redr} \rangle} = \frac{\langle U_e \rangle}{\left(\frac{\langle U_s \rangle}{2 \cdot D}\right)} < 1$$

Fonction de transfert continue :

$$G_{DC} = \frac{\langle U_s \rangle}{\langle U_e \rangle} = \frac{2 \cdot D}{n} = \frac{\langle I_e \rangle}{\langle I_s \rangle}$$

Rapport cyclique:

$$D = \frac{n \cdot \langle U_s \rangle}{2 \cdot \langle U_e \rangle} \le 0.5$$

Déphasage de la commande :

$$\varphi = 2 \cdot \pi \cdot D = \frac{\pi \cdot n \cdot \langle U_s \rangle}{\langle U_o \rangle} \ avec \ \varphi \in [0; \pi]$$

#### 4.1.3.1 Transformateur

Le rapport minimal de transformation est défini d'après la relation suivante :

$$n_{min} = \frac{\langle U_e \rangle_{min}}{\left(\frac{\langle U_s \rangle_{nom}}{2 \cdot D_{max}}\right)}$$

Carreto Romain

Comme défini dans le chapitre 4.1.1, la valeur de l'inductance de magnétisation minimale est définie selon l'équation suivante :

$$L_{h,min} = \frac{U_{e,max} \cdot D_{min}}{\Delta I_{L_h,max} \cdot f_{com}}$$

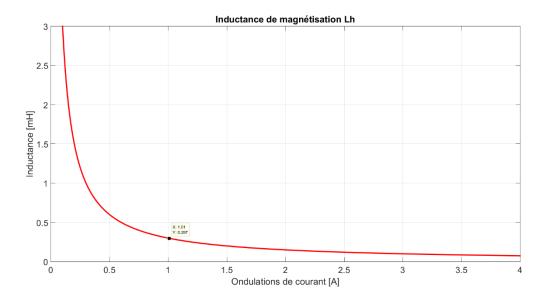

En faisant varier les ondulations de courant, il est possible de réaliser un abaque représentant la valeur de l'inductance en fonction des ondulations de courant :

Figure 27 : Inductance de magnétisation en fonction de l'ondulation de courant

Pour des ondulations en courant de 0.3[A], la valeur minimale nécessaire pour l'inductance vaut :

$$L_{h,min} = 0.8[mH]$$

Il convient de noter que le transformateur ne sert pas à stocker de l'énergie. Les ondulations sur l'inductance de magnétisation doivent être minimale donc l'inductance magnétisante maximale.

Carreto Romain 26 / 93

#### 4.1.3.2 Inductance de sortie L

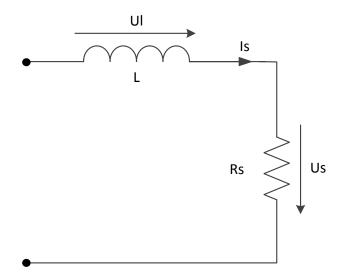

Afin de définir la valeur la plus appropriée pour l'inductance de sortie L, le minimum est calculé pour assurer un fonctionnement en mode continu ( $I_L > 0[A]$ ). Le schéma suivant représente la sortie du chargeur DC/DC :

Figure 28 : Schéma équivalent pour la sortie du système

La batterie constituant la charge est représentée comme étant une résistance. Sa valeur maximale peut être définie comme suit :

$$R_{load,max} = \frac{U_S}{I_{S,min}}$$

La constante de temps du système RL en sortie vaut :

$$\tau_{min} = \frac{L_{min}}{R_{load,max}} <=> L_{min} = R_{load,max} \cdot \tau_{min}$$

Donc:

$$L_{min} = R_{load,max} \cdot \left[ \left( \frac{1}{2} - D_{min} \right) \cdot T \right] = R_{load,max} \cdot \left[ \left( \frac{1}{2} - D_{min} \right) \cdot \frac{1}{f_{com}} \right]$$

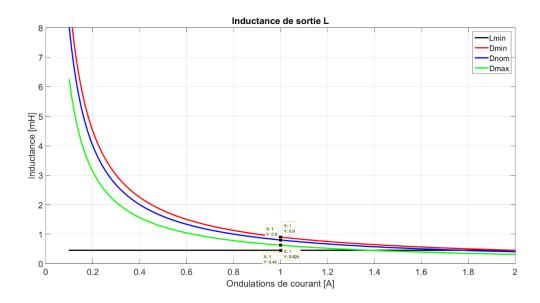

Cette valeur est la limite minimale à considérer. Comme la valeur d'inductance est aussi fonction des ondulations de courant en sortie, il est possible de définir un abaque afin de choisir la valeur d'inductance optimale :

$$L = \frac{U_s}{\Delta I_L \cdot f_{com}} \cdot \left(\frac{1}{2} - D\right)$$

L'abaque suivant représente la valeur d'inductance en fonction des ondulations de courant. Trois rapports cycliques sont considérés :

$$D_{min} = \frac{n \cdot \langle U_s \rangle}{2 \cdot \langle U_e \rangle_{max}} = \frac{0.2 \cdot 48}{2 \cdot 48} = 0.1$$

Carreto Romain 27 / 93

$$D_{nom} = \frac{n \cdot \langle U_S \rangle}{2 \cdot \langle U_e \rangle_{nom}} = \frac{0.2 \cdot 48}{2 \cdot 24} = 0.2$$

$$D_{max} = \frac{n \cdot \langle U_s \rangle}{2 \cdot \langle U_e \rangle_{min}} = \frac{0.2 \cdot 48}{2 \cdot 12} = 0.4$$

#### L'abaque est le suivant :

Figure 29 : Inductance de sortie en fonction des ondulations du courant de sortie

Le rapport cyclique  $D_{min}$  constitue le cas où les ondulations de courant sont maximales. Une valeur de L=1[mH] assure des ondulations maximales de courant de 1[A] dans la charge.

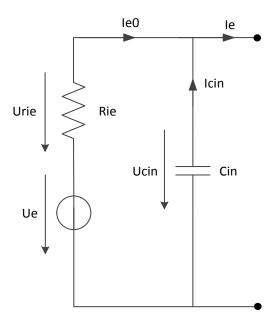

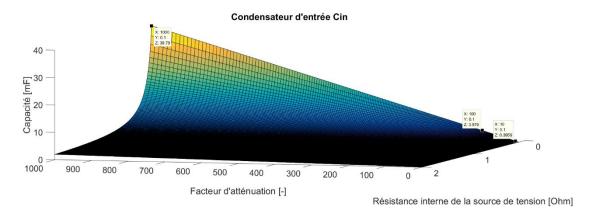

#### 4.1.3.3 Condensateur d'entrée C<sub>in</sub>

Le condensateur d'entrée permet de lisser le courant prélevé à la source de tension en fournissant les ondulations de courant demandées. En effet, le courant est saccadé comme représenté sur la Figure 22.

Le schéma équivalent est le suivant :

Figure 30 : Schéma équivalent pour la source

La fonction de transfert à considérer est donc :

$$F(s) = \frac{I_{e0}(s)}{I_{e}(s)}$$

Il s'agit d'un diviseur de courant :

$$I_e(s) \cdot \frac{\frac{1}{s \cdot C_{in}}}{\frac{1}{s \cdot C_{in}} + R_{i_e}} = I_{e0}(s)$$

La fonction de transfert devient alors :

$$F(s) = \frac{1}{1 + s \cdot C_{in} \cdot R_{i_e}}$$

Il s'agit donc d'un filtre passe-bas du premier ordre. Il est donc possible de définir la valeur de capacité en fonction de la résistance interne de la source ainsi que de l'atténuation souhaitée :

$$||F|| = \frac{1}{K} = \frac{1}{\sqrt{1^2 + \left(2 \cdot \pi \cdot 2 \cdot f_{com} \cdot C_{in} \cdot R_{i_e}\right)^2}}$$

Carreto Romain 29 / 93

Ce qui donne en isolant  $C_{in}$ :

$$C_{in} = \frac{\sqrt{K^2 - 1}}{4 \cdot \pi \cdot f_{com} \cdot R_{i_e}}$$

Avec : K : f acteur d' atténuation,  $f_{com}$  : F réquence de commutation du pont en h

En variant les paramètres :  $K \in [1;1000]$  [-],  $R_{i_e} \in [0.01;2][\Omega]$ , il est possible de définir un abaque pour le choix de la capacité  $C_{in}$  :

Figure 31 : Capacité d'entrée en fonction du facteur d'atténuation et de la résistance interne de la source de tension

La capacité maximale pour une atténuation de 1000x est :

$$C_{in.max} = 40 [mF]$$

La capacité maximale pour une atténuation de 10x est :

$$C_{in.max} = 0.4 [mF]$$

La valeur optimale se situe donc entre  $0.4 \ et \ 40 [mF]$ .

Afin de définir la valeur du condensateur, il est possible de définir les ondulations de courant qu'il doit pouvoir fournir. Le courant total demandé par le système est  $I_e$ . Il peut être décomposé en une partie continue  $I_{e0}$  et des ondulations  $I_{Cin}$  (Cf. Figure 30)°:

$$I_{Cin} = I_{\rho} - I_{\rho 0}$$

Dans le pire des cas (boucle ouverte, déphasage de  $180^{\circ}$ ), le courant RMS  $I_{e0,RMS}$  vaut environ 55[A].

A l'aide de la relation suivante, il est possible de définir la valeur de la capacité  $C_{in}$ :

$$I_{C_{in}} = C_{in} \cdot \frac{dU_{C_{in}}}{dt} <=> C_{in} = \frac{I_{C_{in}} \cdot \frac{T}{2}}{0.1 \cdot U_{e,min}} = \frac{55 \cdot 25 \cdot 10^{-6}}{0.1 \cdot 24} = 573[\mu F]$$

En limitant les ondulations de tension d'entrée à 10[%] de sa valeur minimale soit 2.4[V], la valeur de capacité doit valoir  $573[\mu F]$  au minimum.

Carreto Romain 30 / 93

#### 4.1.4 Contrôle par simulation

Les éléments principaux du dispositif ont été définis en considérant un système idéal. Il s'agit cidessous de montrer les différences que le système réel. Chaque composant est modélisé par son schéma équivalent (cf. Chapitre « Modèles pour le calcul des pertes »).

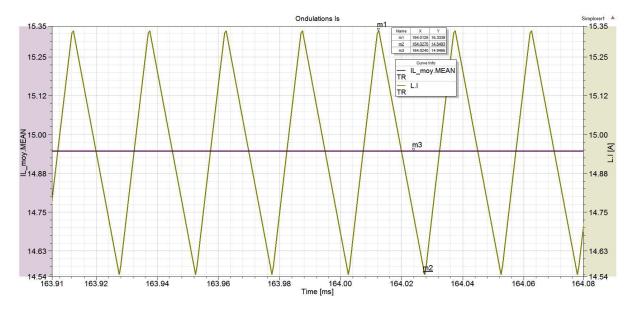

#### 4.1.4.1 Ondulations de courant en sortie

Les ondulations maximales en sortie surviennent lorsque le déphasage vaut  $180^\circ$  avec une tension d'entrée de 24[V] :

Figure 32 : Ondulations maximales de courant en sortie du chargeur

Il existe uniquement deux manières de réduire les ondulations (courbe verte ci-dessus) par rapport à la valeur moyenne de courant (courbe violette ci-dessus) : augmenter la fréquence de commutation du pont en H ou augmenter la valeur de l'inductance de sortie.

Il faut savoir qu'une augmentation de la fréquence de commutation augmente les pertes par commutations ; un compromis doit alors être déterminé.

Pour la valeur de l'inductance, l'augmentation de sa valeur engendre l'augmentation de son volume mécanique. Une valeur optimale est également à déterminer.

Sans régulation le système ne peut pas fonctionner : si la valeur moyenne de tension en sortie du redresseur à diodes est plus grande que 48[V], la tension sur l'inductance de sortie est non nulle et le courant ne cessera d'augmenter (il est tout de même limité par les résistances internes au circuit). Dans le cas où la tension moyenne en sortie du redresseur est inférieure à 48[V], la tension sur l'inductance sera négative et le courant tendra vers 0[A]. Il est donc nécessaire de réguler le courant de sortie.

Carreto Romain 31 / 93

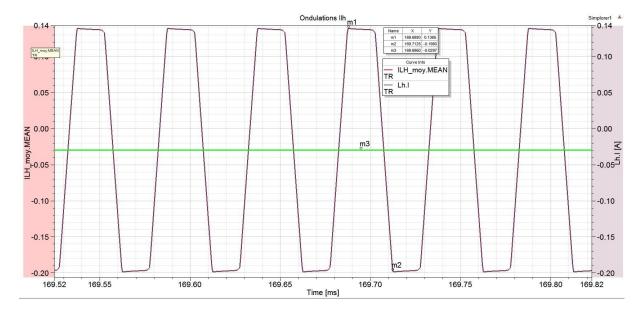

#### 4.1.4.2 Ondulation sur l'inductance de magnétisation du transformateur

Les ondulations maximales sur l'inductance de magnétisation  $L_h$  surviennent lorsque le déphasage vaut  $180^\circ$  avec une tension d'entrée de 24[V] :

Figure 33 : Ondulations maximales de courant sur l'inductance de magnétisation du transformateur  $L_h$

Le courant magnétisant (courbe violette ci-dessus) ondule autour d'une valeur moyenne de 0[A]. Sans régulation, cette valeur moyenne peut s'éloigner de la valeur nulle risquant de saturer le noyau ferromagnétique du transformateur.

En considérant le système comme idéal, les ondulations de courant magnétisant sont croissantes, décroissantes ou constantes. Sur la figure ci-dessus, la courbe décroit légèrement au lieu d'être constante ; cela est dû à l'effet résistif des bobines du transformateur.

Pour un couplage idéal, la valeur de l'inductance de magnétisation doit être maximale afin de minimiser le courant magnétisant et donc le stockage d'énergie dans le transformateur. En pratique cette valeur est limitée par la fabrication du transformateur. Une valeur trop importante entrainerait une taille excessive du transformateur. Il s'agit alors de définir la valeur minimale nécessaire au bon fonctionnement du système.

#### 4.1.4.3 Courant prélevé à la source

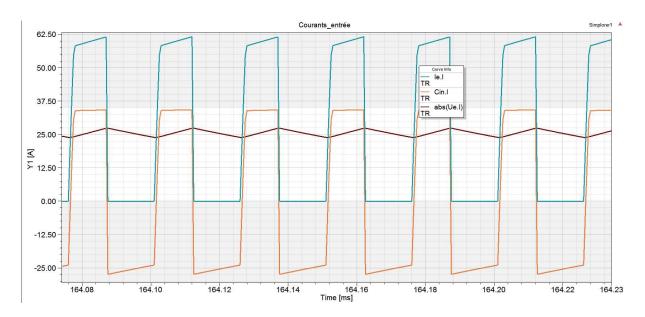

Le condensateur en entrée  $C_{in}$  permet de fournir les ondulations de courant demandées par le système afin d'éviter des variations trop importantes de courant sur la source. Le courant demandé par le système  $I_e$ , fourni par le condensateur  $I_{C_{in}}$  ainsi que par la source  $I_{e0}$  dans le pire des cas (déphasage de  $180^\circ$ ) possèdent les formes suivantes :

Carreto Romain 32 / 93

Figure 34 : Courants du côté de la source de tension du système

Sur la figure ci-dessus, la courbe bleue représente le courant prélevé par le système, la courbe pourpre, le courant prélevé à la source de tension et la courbe orange, le courant délivré par le condensateur.

La capacité du condensateur vaut dans ce cas 1[mF]. Le condensateur se charge par la source de tension lorsque le système ne demande pas de courant puis délivre le maximum de courant qu'il peut lorsque le système souhaite prélever du courant. Cela permet de diminuer les ondulations de courant demandées à la source. Dans ce cas le courant prélevé à la source est de valeur moyenne de 25[A] avec des ondulations de +/-2.5[A] (cas critique).

## 4.1.5 Valeurs numériques

Ci-dessous, le Tableau 2 regroupe toutes les valeurs numériques liées aux équations définies cidessus. Il est à noter que le rendement du dispositif est considéré comme unitaire dans un premier temps pour faciliter l'étude de la topologie.

| N° | Désignation                  | Variable                    | Valeur | Unité        |

|----|------------------------------|-----------------------------|--------|--------------|

| 1  | Tension d'entrée minimale    | $< U_{e,min} >$             | 24     | [V]          |

| 2  | Tension d'entrée nominale    | $\langle U_{e,nom} \rangle$ | 36     | [V]          |

| 3  | Tension d'entrée maximale    | $< U_{e,max} >$             | 48     | [ <i>V</i> ] |

| 4  | Tension de sortie nominale   | $\langle U_{s,nom} \rangle$ | 48     | [V]          |

| 5  | Courant de sortie minimal    | $\langle I_{s,min} \rangle$ | 2      | [ <i>A</i> ] |

| 6  | Courant de sortie maximal    | $\langle I_{s,max} \rangle$ | 8      | [ <i>A</i> ] |

| 7  | Fréquence de commutation     | $f_{com}$                   | 20     | [kHz]        |

| 8  | Puissance de sortie minimale | $< P_{s,min} >$             | 96     | [W]          |

| 9  | Puissance de sortie maximale | $< P_{s,max} >$             | 384    | [W]          |

| 10 | Puissance d'entrée minimale  |                             |        | [W]          |

| 11 | Puissance d'entrée maximale  | $< P_{e,max} >$             | 384    | [W]          |

| 12 | Courant d'entrée minimal     | $\langle I_{e,min} \rangle$ | 2      | [A]          |

| 13 | Courant d'entrée maximal     | $< I_{e,max} >$             | 16     | [ <i>A</i> ] |

| 14 | Charge minimale en sortie    | $R_{load,min}$              | 6      | $[\Omega]$   |

| 15 | Charge maximale en sortie    | $R_{load,max}$              | 24     | $[\Omega]$   |

Carreto Romain 33 / 93

| 16 | Charge minimale en entrée                                                               | $R_{e,min}$         | 1.5             | $[\Omega]$   |

|----|-----------------------------------------------------------------------------------------|---------------------|-----------------|--------------|

| 17 | Charge maximale en entrée                                                               | $R_{e,max}$         | 24              | $[\Omega]$   |

| 18 | Gain moyen minimal                                                                      | $G_{DC,min}$        | 1               | [-]          |

| 19 | Gain moyen nominal                                                                      | $G_{DC,nom}$        | 1.33            | [-]          |

| 20 | Gain moyen maximal                                                                      | $G_{DC,max}$        | 2               | [-]          |

| 21 | Rapport de transformation maximal                                                       | $n_{max}$           | 0.25            | [-]          |

| 22 | Rapport cyclique minimal                                                                | $D_{min}$           | 0.125           | [-]          |

| 23 | Rapport cyclique nominal                                                                | $D_{nom}$           | 0.167           | [-]          |

| 24 | Rapport cyclique maximal                                                                | $D_{max}$           | 0.25            | [-]          |

| 25 | Déphasage minimal                                                                       | $arphi_{min}$       | $\frac{\pi}{4}$ | [rad]        |

| 26 | Déphasage minimal en degrés                                                             | $arphi_{min,deg}$   | 45              | [°]          |

| 27 | Déphasage nominal                                                                       | $arphi_{nom}$       | $\frac{\pi}{3}$ | [rad]        |

| 28 | Déphasage nominal en degrés                                                             | $arphi_{nom,deg}$   | 60              | [°]          |

| 29 | Déphasage maximal                                                                       | $arphi_{max}$       | $\frac{\pi}{2}$ | [rad]        |

| 30 | Déphasage maximal en degrés                                                             | $arphi_{max,deg}$   | 90              | [°]          |

| 31 | Inductance de sortie                                                                    | L                   | 1               | [mH]         |

| 32 | Ondulations maximales de courant sur l'inductance de sortie                             | $\Delta I_{L,max}$  | 0.9             | [ <i>A</i> ] |

| 33 | Courant maximal dans l'inductance de sortie                                             | $I_{L,max}$         | 8.45            | [ <i>A</i> ] |

| 34 | Inductance de magnétisation                                                             | $L_h$               | 1               | [mH]         |

| 35 | Ondulations maximales de courant sur l'inductance de magnétisation $\Delta I_{L_h,max}$ |                     | 0.3             | [ <i>A</i> ] |

| 36 | Condensateur d'entrée                                                                   | $C_{in}$            | 1               | [mF]         |

| 37 | Ondulations maximales de courant en entrée                                              | $\Delta I_{e0,max}$ | 3.395           | [ <i>A</i> ] |

| 38 | Tension maximale sur le condensateur d'entrée                                           | $U_{C_{in},max}$    | 48              | [ <i>V</i> ] |

| 39 | Tension maximale sur les interrupteurs                                                  | $U_{T,max}$         | 48              | [V]          |

| 40 | Courant maximal dans les interrupteurs                                                  | $I_{T,max}$         | 33.95           | [ <i>A</i> ] |

| 41 | Tension maximale sur les diodes en antiparallèle des interrupteurs                      | $U_{D,max}$         | 48              | [V]          |

| 42 | Courant maximal dans les diodes en antiparallèle des interrupteurs                      | $I_{D,max}$         | 33.95           | [A]          |

| 43 | Tension maximale sur le transformateur                                                  | $U_{trafo,max}$     | 192             | [V]          |

| 44 | Courant maximal dans le transformateur                                                  | $I_{trafo,max}$     | 33.95           | [A]          |

| 45 | Tension maximale sur les diodes du redresseur                                           | $U_{Dredr,max}$     | 192             | [V]          |

| 46 | Courant maximal dans les diodes du redresseur                                           | $I_{Dredr,max}$     | 8.45            | [ <i>A</i> ] |

Tableau 2 : Récapitulatif des valeurs du système en fonctionnement normal

Le calcul des valeurs se trouve sous « Annexe 2 : Scripts Matlab°».

Les valeurs (inductances, condensateur et transformateur) peuvent être sujettes à de faibles variations pour améliorer certains paramètres tels que le prix ou la taille.

Les valeurs du tableau ci-dessus font référence au système lorsqu'il fonctionne comme prévu. Pour les valeurs critiques sur les éléments du système il faut considérer le pire des cas (déphasage de  $180^{\circ}$ ). Ce cas est traité plus tard dans le rapport.

Carreto Romain 34 / 93

### Remarque importante :

La tension minimale d'entrée était de 12[V] selon le cahier des charges établi au début du projet. Cette valeur a été augmentée à 24[V]. La raison principale est que les contraintes en courant sont importantes au primaire du transformateur. La faible tension d'entrée ajoutée aux forts courants impose des pertes et chutes de tension considérable sur les composants. La tension utile au primaire du transformateur est alors trop faible pour permettre de réguler correctement le dispositif. Des simulations au chapitre « Phase 3 : » permettent de confirmer ce choix.

## 4.1.6 Modèles pour le calcul des pertes

Ce chapitre donne les équations fondamentales liées aux pertes de chaque composant du système. Celles-ci seront appliquées lorsque les caractéristiques des composants seront connues.

### 4.1.6.1 **Diodes**

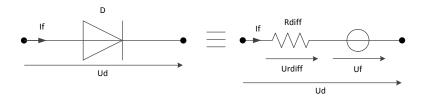

Le modèle équivalent de la diode est :

Figure 35 : Schéma équivalent de la diode

Les pertes qui y sont liés sont dues uniquement à la conduction. Les pertes sont définies par la relation suivante :

$$P_{cond} = U_f \cdot I_{f_{moven}} + R_{diff} \cdot I_{f_{RMS}}^2[W]$$

## 4.1.6.2 Interrupteurs

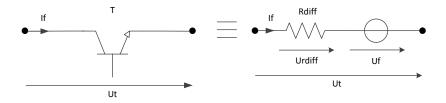

Le modèle équivalent des interrupteurs à considérer est :

Figure 36 : Schéma équivalent de l'interrupteur

Les pertes y sont de deux natures différentes : pertes par conduction et par commutation. Pour les pertes par conduction l'équation à considérer est la suivante :

$$P_{cond} = U_f \cdot I_{fmoyen} + R_{diff} \cdot I_{f_{RMS}}^2[W]$$

Carreto Romain 35 / 93

Pour les pertes par commutations, il est possible de définir les pertes à partir de l'énergie d'enclenchement et de déclenchement en connaissant les temps de commutations :

$$P_{on} = E_{on} \cdot t_{on}$$

$P_{off} = E_{off} \cdot t_{off}$   $P = P_{on} + P_{off}$

### 4.1.6.3 Condensateur

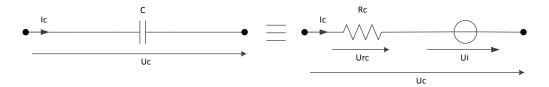

Le modèle considéré pour les pertes est le suivant :

Figure 37 : Schéma équivalent du condensateur

Pour le condensateur, les pertes sont essentiellement dues à la résistance équivalente série du condensateur (en Anglais : ESR). Les pertes sont obtenues grâce à l'équation suivante :

$$P = R_C \cdot I_{C_{RMS}}^2[W]$$

### **4.1.6.4** *Inductance*

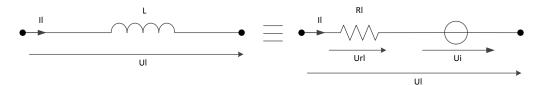

Le modèle considéré pour les pertes est le suivant :

Figure 38 : Schéma équivalent de l'inductance

Pour l'inductance, les pertes sont essentiellement dues à la résistance du cuivre composant la bobine. Les pertes sont obtenues grâce à l'équation suivante :

$$P = R_L \cdot I_{L_{RMS}}^2[W]$$

## 4.1.6.5 Transformateur

Le schéma équivalent complet pour le transformateur est le suivant :

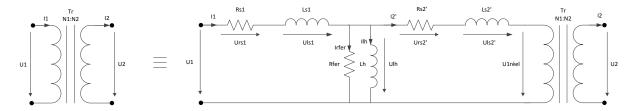

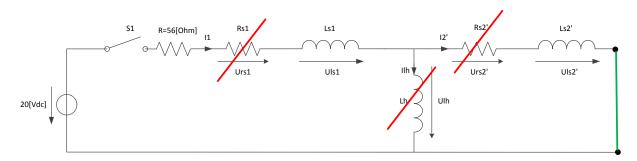

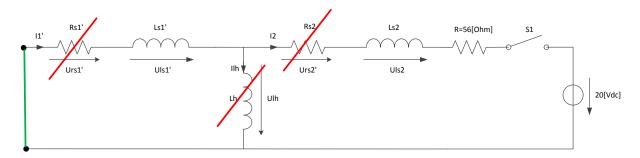

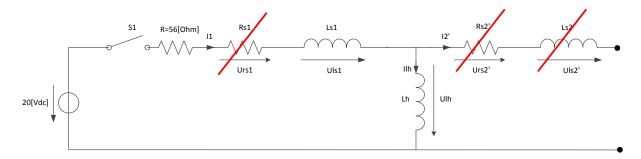

Figure 39 : Schéma équivalent du transformateur

Carreto Romain 36 / 93

Les pertes sont essentiellement dues aux résistances des bobinages :

$$P = R_{S_1} \cdot I_{1_{RMS}}^2 + R_{S_2'} \cdot I_{2'_{RMS}}^2 [W]$$

### 4.1.6.6 Sources de tension

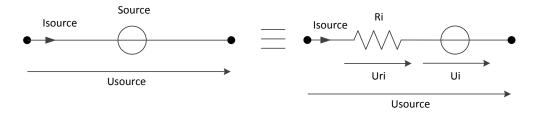

Les sources de tension ne sont pas idéales et peuvent être définies selon le schéma suivant :

Figure 40 : Schéma équivalent pour la source de tension

Les pertes sont dues à la résistance série et valent :

$$P = R_i \cdot I_{source_{moven}}^2$$

# 4.2 Régulation du dispositif

La régulation permet de contrôler deux paramètres du dispositif :

- 1. Le courant de sortie : le chargement de la batterie peut alors est contrôlée de manière précise.

- 2. Le courant magnétisant du transformateur : il est nécessaire de garantir un courant magnétisant moyen nul afin d'éviter la saturation du noyau magnétique.

Un schéma de principe permet de visualiser le dispositif ainsi que les boucles de régulations qui y sont attachées.

Ensuite chaque régulation est analysée de manière indépendante moyennant la mise en équation, la simulation de la boucle de réglage afin de déterminer le type et les paramètres de chaque régulateur.

La régulation se concentre sur les valeurs moyennes du système.

Carreto Romain 37 / 93

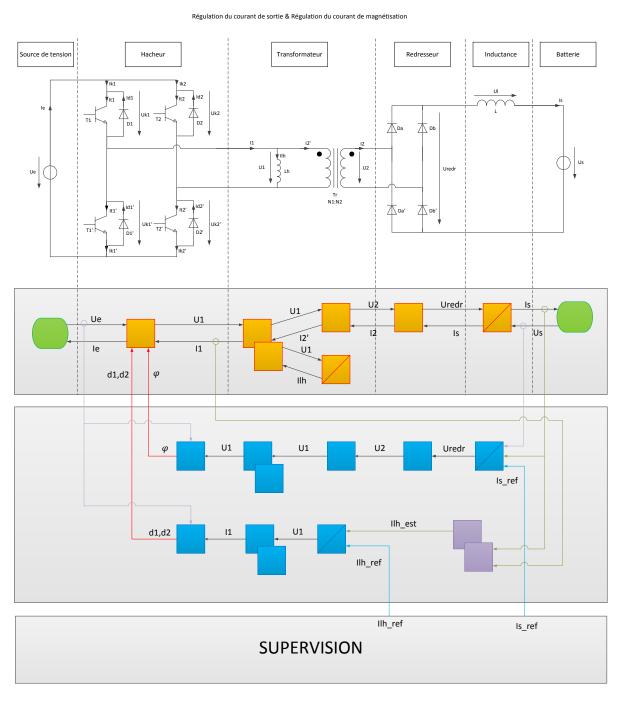

# 4.2.1 Schéma de principe

Le schéma de principe ci-dessous est aussi appelé « Energetic Macroscopic Representation and control » (EMR). Il représente les relations de cause à effet du système. La régulation peut alors également être représentée.

Figure 41 : Schéma de principe du système et de sa régulation (EMR)

La topologie est divisée en étapes de transformation. La tension appliquée au transformateur agit sur deux paramètres distincts : le courant de sortie et le courant magnétisant. C'est pourquoi le flux se sépare en deux branches parallèles. Les deux boucles de régulation sont représentées par la couleur bleue.

Carreto Romain 38 / 93

Le système dispose de deux degrés de liberté pour le contrôler :

- 1. Le déphasage entre les deux bras du pont complet, noté  $\phi$ , qui permet de contrôler le courant de sortie du dispositif.

- 2. Le rapport cyclique de chaque bras du pont complet, noté  $d_1$  et  $d_2$ , qui permet le contrôle du courant magnétisant du transformateur (les rapports cycliques varient autour de 0.5).

### 4.2.2 Régulation du courant de sortie

Ci-dessous, uniquement la boucle de régulation du courant de sortie est représentée. Une modélisation locale peut être réalisée afin de dimensionnement le régulateur.

## 4.2.2.1 Equations liées à la régulation du dispositif

Modélisation du courant de sortie en fonction des paramètres de contrôle du système :

$$U_L = U_{redr} - U_s = \frac{U_e \cdot 2 \cdot D}{n} - U_s = \frac{U_e \cdot 2 \cdot \frac{\varphi}{2 \cdot \pi} \cdot \frac{\pi}{180}}{n} - U_s \ avec \ \varphi \ [deg]$$

La simplification donne :

$$U_L = \frac{U_e}{180 \cdot n} \cdot \varphi - U_s \quad (1)$$

La relation courant-tension pour l'inductance de sortie vaut :

$$I_L = \frac{1}{L} \cdot \int_0^T U_L \cdot dt$$

Dans le domaine de Laplace, la relation est :

$$I_L(s) = \frac{1}{L} \cdot \frac{1}{s} \cdot U_L(s) = \frac{U_L(s)}{s \cdot L}$$

La relation entre le courant de sortie et le déphasage devient donc :

$$I_L = \frac{1}{s \cdot L} \cdot \left[ \frac{U_e}{180 \cdot n} \cdot \varphi - U_s \right]$$

A partir de la relation (1) ci-dessus, il est possible de déterminer la structure de réglage en l'inversant :

$$\varphi = (U_L + U_S) \cdot \frac{180 \cdot n}{U_{\rho}}$$

Le régulateur possède la fonction de transfert suivante :

$$Rég(s) = \frac{U_L(s)}{e(s)} = \frac{U_L(s)}{(I_{L,ref}(s) - I_{L,mes}(s))}$$

Carreto Romain 39 / 93

## 4.2.2.2 Dimensionnement du régulateur

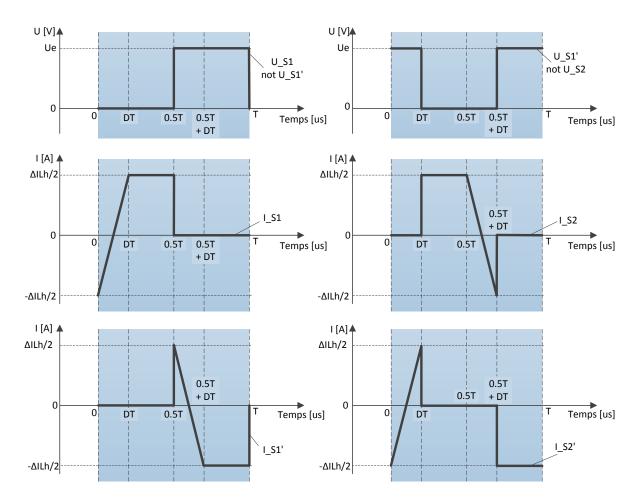

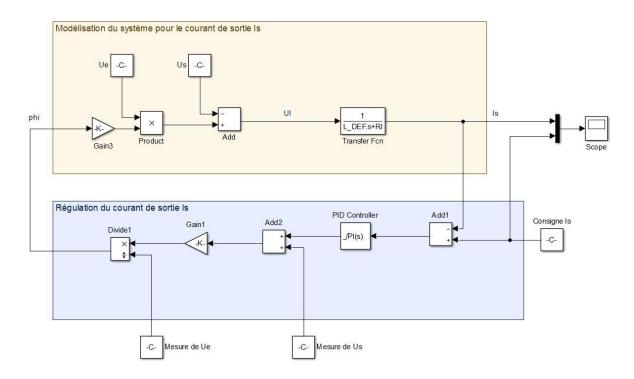

A partir des relations ci-dessus, il est possible de modéliser le système et la boucle de réglage afin de dimensionner le régulateur :

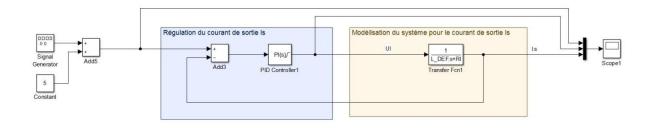

Figure 42 : Modélisation et régulation du système pour le courant de sortie Is

Le schéma ci-dessus possède l'avantage de pouvoir visualiser les valeurs internes de la régulation comme le déphasage  $\varphi$ . Pour la définition des paramètres du régulateur, un schéma simplifié suffit.

Le schéma peut alors être simplifié comme suit :

Figure 43 : Modélisation et régulation du système pour le courant de sortie Is (simplifié)

Pour la régulation du courant de sortie, un régulateur de type PI est choisi. Le fait que la régulation se concentre sur le courant moyen implique que la dynamique du courant reste lente et ne nécessite pas de régulation de type D. De plus, le système considéré est d'ordre 1 et il convient donc de le réguler par un régulateur du même ordre.

Carreto Romain 40 / 93

La fonction de transfert en boucle fermée est :

$$F_{CL}(s) = \frac{R\acute{e}g(s) \cdot F(s)}{1 + R\acute{e}g(s) \cdot F(s)} = \frac{\frac{K_P \cdot (1 + s \cdot T_i)}{s \cdot T_i} \cdot \frac{1}{R_L + s \cdot L}}{1 + \frac{K_P \cdot (1 + s \cdot T_i)}{s \cdot T_i} \cdot \frac{1}{R_L + s \cdot L}}$$

Remarque : La résistance propre à l'inductance  $R_L$  est prise en compte pour la modélisation du système.

Premièrement la constante de temps dominante (unique dans ce cas) est compensée :

$$1 + s \cdot T_i = 1 + s \cdot \frac{L}{R_L}$$

Donc:

$$T_i = \frac{L}{R_I}$$

La fonction de transfert en boucle fermée devient :

$$F_{CL}(s) = \frac{\frac{K_P}{s \cdot T_i} \cdot \frac{\frac{1}{R_L}}{1}}{1 + \frac{K_P}{s \cdot T_i} \cdot \frac{1}{R_L}} = \frac{\frac{K_P}{s \cdot L}}{1 + \frac{K_P}{s \cdot L}} = \frac{1}{1 + s \cdot \frac{L}{K_P}}$$

La constante de temps du système en boucle fermée vaut :

$$\tau_{CL} = \frac{L}{K_P}$$

Plus le gain  $K_P$  du régulateur est grand, plus le système régulé sera rapide. Le gain est toutefois limité par la tension maximale applicable sur l'inductance de sortie. Cette tension maximale vaut :

$$U_{L,max} = \frac{U_{e,max}}{180 \cdot n} \cdot \varphi_{max} - U_s = \frac{48}{180 \cdot 0.25} \cdot 180 - 48 = 144[V]$$

Le même effet a lieu pour la tension minimale applicable sur l'inductance de sortie. La tension minimale vaut :

$$U_{L,min} = -U_{s} = -48[V]$$

La plage de tension applicable à l'inductance de sortie n'est donc pas symétrique. Afin de garantir une régulation symétrique autour de la consigne donnée, il est nécessaire de définir le gain maximal par rapport à la tension absolue minimale soit  $U_{L,min} = -48[V]$ .

Carreto Romain 41 / 93

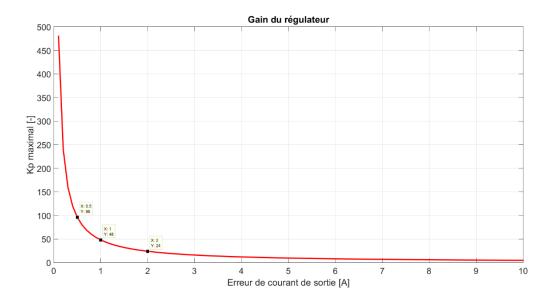

Un abaque représentant le gain  $\mathcal{K}_P$  en fonction de l'erreur de courant peut être établi :

Figure 44 : Gain maximal du régulateur en fonction de l'erreur du courant de sortie

Plus l'erreur en entrée du régulateur est grande, plus le gain maximal est limité, ceci afin d'éviter la saturation.

Un critère pour le choix du gain  $K_P$  (En respectant l'abaque de la Figure 44) est la rapidité du système en boucle fermée. Il est possible alors de poser le critère suivant :

$$\tau_{CL} = \frac{\tau_{OL}}{x} \ avec \ x \in [2; 100]$$

Si, par exemple,

$$x=100$$

alors  $au_{CL}=rac{ au_{OL}}{10}=rac{0.01}{100}=0.0001[s]$  et donc  $K_P=rac{L}{ au_{CL}}=rac{0.001}{0.0001}=10$ .

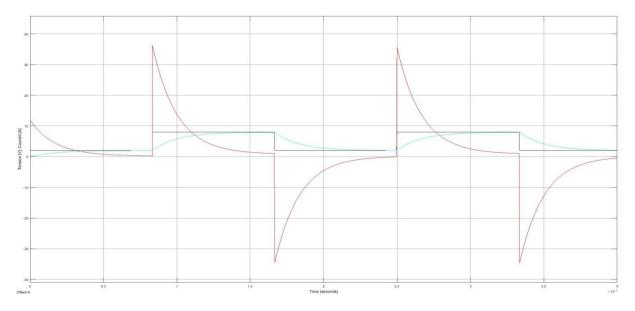

Pour une consigne de courant variant entre 2 et 8[A] et avec un  $K_P = 6$  (le gain maximal avant saturation pour une erreur de 6[A] est 8 selon la Figure 44) et un  $T_i = 10[ms]$ , la simulation donne :

Figure 45 : Réponse du courant de sortie en boucle fermée sans saturation du régulateur

Carreto Romain 42 / 93

En noir, la consigne de courant ; en rouge, la tension appliquée sur l'inductance de sortie (sortie du régulateur) et en bleu le courant de sortie régulé  $I_s$ . L'intégrateur supprime l'écart permanent alors que le gain du régulateur permet une convergence rapide vers la consigne. Il n'y a pas de saturation du régulateur.

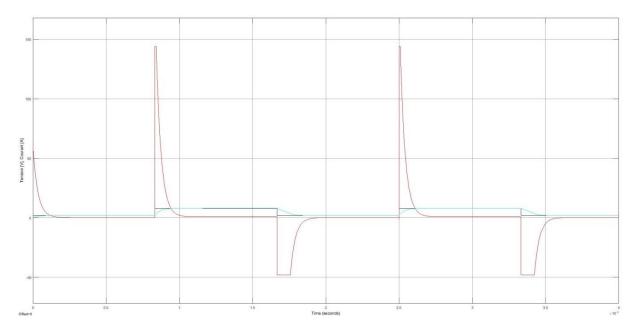

Le graphe suivant montre la saturation du régulateur pour un gain  $K_P$  trop élevé :

Figure 46 : Réponse du courant de sortie en boucle fermée avec saturation du régulateur

La courbe rouge qui représente la sortie du régulateur mais aussi la tension à appliquer à l'inductance de sortie subit des saturations dues aux limites du système (Figure 46). Cette saturation implique un ralentissement du dispositif de régulation par rapport au dimensionnement effectué ce qui peut affecter la stabilité du système.

### 4.2.3 Régulation du courant magnétisant

Ci-dessous, uniquement la boucle de régulation du courant magnétisant est représentée. Une modélisation locale peut être réalisée afin de dimensionnement le régulateur.

# 4.2.3.1 Equations liées à la régulation du dispositif

Modélisation du courant de magnétisation du transformateur en fonction des paramètres de contrôle du système :

$$U_{L_h} = U_1 = U_A - U_B = d_1 \cdot U_e - d_2 \cdot U_e = (d_1 - d_2) \cdot U_e$$

(2)

La relation courant-tension pour l'inductance de magnétisation vaut :

$$I_{L_h} = \frac{1}{L_h} \cdot \int_0^T U_{L_h} \cdot dt$$

Dans le domaine de Laplace, la relation est :

$$I_{L_h}(s) = \frac{1}{L_h} \cdot \frac{1}{s} \cdot U_{L_h}(s) = \frac{U_{L_h}(s)}{s \cdot L_h}$$

Carreto Romain 43 / 93

La relation entre le courant de sortie et le rapport cyclique du deuxième bras du pont complet  $d_2$  devient donc (Le rapport cyclique  $d_1$  est fixé à 0.5) :

$$I_{L_h} = \frac{1}{s \cdot L_h} \cdot [(d_1 - d_2) \cdot U_e]$$

A partir de la relation (2) ci-dessus, il est possible de déterminer la structure de réglage en l'inversant :

$$d_2 = \frac{1}{2} - \frac{U_{L_h}}{U_e}$$

Le régulateur possède la fonction de transfert suivante :

$$R\acute{e}g(s) = \frac{U_{L_h}(s)}{e(s)} = \frac{U_{L_h}(s)}{(I_{L_{L_h,ref}}(s) - I_{L_h,mes}(s))} = \frac{U_1(s)}{(I_{L_h,ref}(s) - I_{1,mes}(s))}$$

Remarque : Le courant mesuré est le courant  $I_1$  au primaire du transformateur car le courant de magnétisation n'est pas directement mesurable sur le système. Le courant  $I_{L_h}$  est également de valeur moyenne nulle, il est donc possible de considérer le courant  $I_1$  plutôt que le courant de magnétisation pour effectuer la régulation.

## 4.2.3.2 Dimensionnement du régulateur

A partir des relations ci-dessus, il est possible de modéliser le système et la boucle de réglage afin de dimensionner le régulateur :

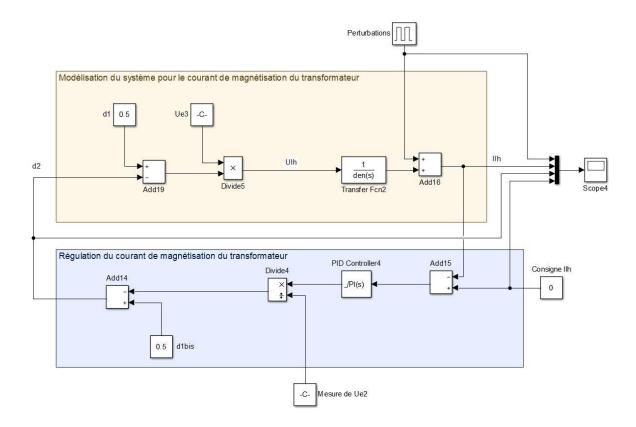

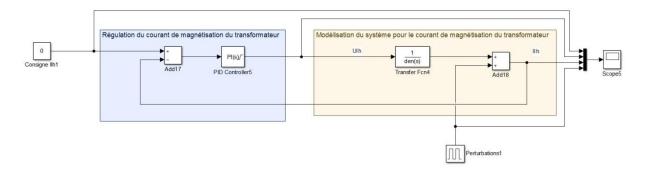

Figure 47 : Modélisation et régulation du système pour le courant de magnétisation  $I_{Lh}$

Carreto Romain 44 / 93

Le schéma ci-dessus possède l'avantage de pouvoir visualiser les valeurs internes de la régulation comme le rapport cyclique  $d_2$ . Pour la définition des paramètres du régulateur, un schéma simplifié suffit.

Le schéma peut alors être simplifié comme suit :

Figure 48 : Modélisation et régulation du système pour le courant de magnétisation IIh (simplifié)

Pour la régulation du courant de magnétisation, un régulateur de type PI est choisi. Le fait que la régulation se concentre sur le courant moyen implique que la dynamique du courant reste lente et ne nécessite pas de régulation de type D.

Le courant étant régulé autour de 0[A], des perturbations (signal carré valant 0 et 0.5[A] avec un rapport cyclique de 50%) sont ajouté à la sortie du système afin de visualiser le travail du régulateur.

La fonction de transfert en boucle fermée est :

$$F_{CL}(s) = \frac{R\acute{e}g(s) \cdot F(s)}{1 + R\acute{e}g(s) \cdot F(s)} = \frac{\frac{K_P \cdot (1 + s \cdot T_i)}{s \cdot T_i} \cdot \frac{1}{R_{L_h} + s \cdot L_h}}{1 + \frac{K_P \cdot (1 + s \cdot T_i)}{s \cdot T_i} \cdot \frac{1}{R_{L_h} + s \cdot L_h}}$$

Remarque : La résistance propre à l'inductance  $R_{L_h}$  est prise en compte pour la modélisation du système.

Premièrement la constante de temps dominante (unique dans ce cas) est compensée :

$$1 + s \cdot T_i = 1 + s \cdot \frac{L}{R_{L_h}}$$

Donc:

$$T_i = \frac{L}{R_{L_h}}$$

Carreto Romain 45 / 93

La fonction de transfert en boucle fermée devient :

$$F_{CL}(s) = \frac{\frac{K_P}{s \cdot T_i} \cdot \frac{1}{R_{L_h}}}{1 + \frac{K_P}{s \cdot T_i} \cdot \frac{1}{R_{L_h}}} = \frac{\frac{K_P}{s \cdot L_h}}{1 + \frac{K_P}{s \cdot L_h}} = \frac{1}{1 + s \cdot \frac{L_h}{K_P}}$$

La constante de temps du système en boucle fermée vaut :

$$\tau_{CL} = \frac{L_h}{K_P}$$

Plus le gain  $K_P$  du régulateur est grand, plus le système régulé sera rapide. Le gain est toutefois limité par la tension maximale applicable sur l'inductance de magnétisation. Cette tension maximale vaut :

$$U_{L_{b},max} = U_{e,max} = 48[V]$$

Le même effet a lieu pour la tension minimale applicable sur l'inductance de magnétisation. La tension minimale vaut :

$$U_{L_h,min} = -U_{e,max} = -48[V]$$

La plage de tension applicable à l'inductance de magnétisation est symétrique.

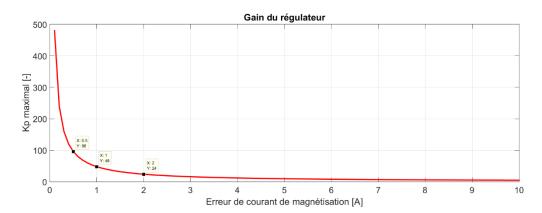

Un abaque représentant le gain  $K_P$  en fonction de l'erreur de courant peut être établi :

Figure 49 : Gain maximal du régulateur en fonction de l'erreur du courant de magnétisation

Plus l'erreur en entrée du régulateur est grande, plus le gain maximal est limité afin d'éviter la saturation.

Un critère pour le choix du gain  $K_P$  (En respectant l'abaque de la Figure 44) est la rapidité du système en boucle fermée. Il est alors possible de poser le critère suivant :

$$\tau_{CL} = \frac{\tau_{OL}}{x}$$

avec  $x \in [2; 100]$

Si, par exemple,

$$x=100$$

alors  $\tau_{CL}=\frac{\tau_{OL}}{100}=\frac{0.01}{100}=0.0001[s]$  et donc  $K_P=\frac{L_h}{\tau_{CL}}=\frac{0.001}{0.0001}=10$ .

Carreto Romain 46 / 93

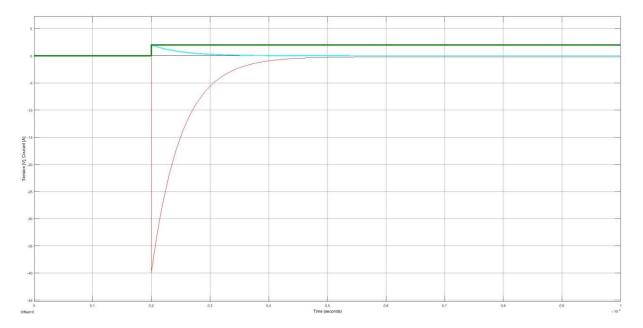

Pour une consigne de courant de 0[A] (nécessaire pour éviter la saturation du transformateur) et avec un  $K_P=20$  (le gain maximal avant saturation pour une erreur de 2[A] est 24 selon la Figure 44) et un  $T_i=10[ms]$ , la simulation nous donne :

Figure 50 : Réponse du courant de magnétisation en boucle fermée sans saturation du régulateur

En noir, la consigne de courant (fixée à 0[A]); en rouge, la tension appliquée sur l'inductance de sortie (sortie du régulateur) et en bleu le courant de sortie régulé  $I_s$ . La courbe verte (saut indiciel) représente une perturbation de 2[A]. L'intégrateur supprime l'écart permanent alors que le gain du régulateur permet une convergence rapide vers la consigne. Il n'y a pas de saturation du régulateur.

Le graphe suivant montre la saturation du régulateur pour un gain  $K_P$  trop élevé :

Figure 51 : Réponse du courant de magnétisation en boucle fermée avec saturation du régulateur

Carreto Romain 47 / 93

La courbe rouge qui représente la sortie du régulateur mais aussi la tension à appliquer à l'inductance de magnétisation (primaire du transformateur) subit des saturations dues aux limites du système. Cette saturation implique un ralentissement du dispositif de régulation par rapport au dimensionnement effectué ce qui peut affecter la stabilité du système.

# 4.2.4 Codage de la régulation

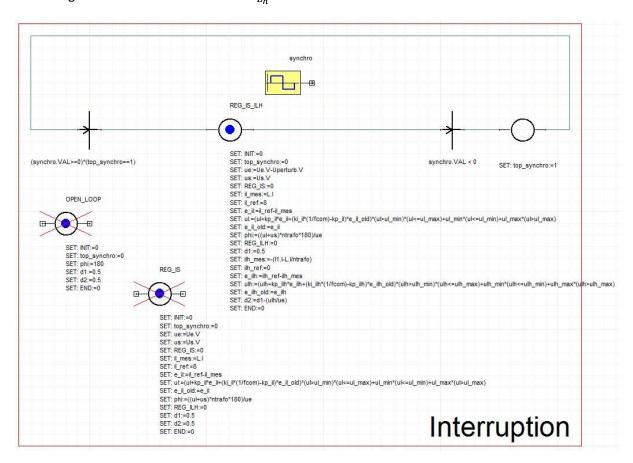

Afin de représenter le système de la manière la plus réaliste possible en simulation, la commande des interrupteurs est à l'image de la commande réelle. Une interruption survient toute les  $50[\mu s]$  afin d'exécuter le code qui commandera les interrupteurs.

Le code retourne une valeur de déphasage  $\varphi$  ainsi que les deux rapports cyclique  $d_1$  et  $d_2$  qui régissent le comportement temporel de chaque bras du pont en H.

Trois codes ont été implémentés : commande du système en boucle ouverte, en boucle fermée pour la régulation du courant de sortie  $I_S$  et en boucle fermée pour la commande du courant de sortie  $I_S$  et de magnétisation du transformateur  $I_{L_h}$ .

Figure 52: Codes et interruption pour la simulation

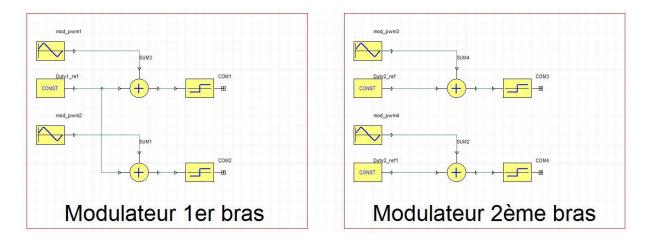

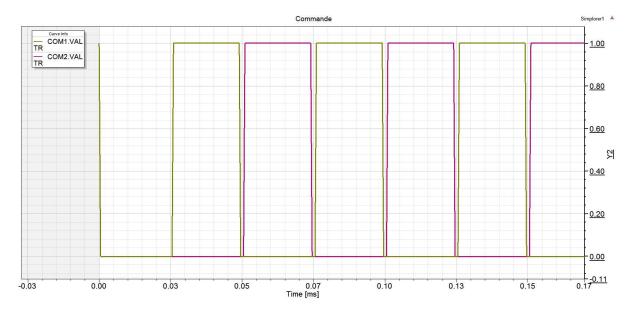

Les signaux de commande des interrupteurs doivent être produits à partir de l'information de déphasage et des rapport cycliques de chaque bras du pont. Pour le réaliser, le rapport cyclique de chaque bras est soustrait à un signal triangulaire d'amplitude 1 (le signal varie entre 0 et 1) et de période  $50[\mu s]$ . Si la valeur résultante est inférieure à 0.5, l'interrupteur du bas du bras conduit, si le signal est supérieur à 0.5 c'est l'interrupteur du haut qui conduit.

Carreto Romain 48 / 93

Figure 53: Simulation de la commande des interrupteurs

Pour déphaser les deux bras, il suffit de déphaser les deux signaux triangulaires propre à chaque bras du pont.

Afin de visualiser les courants inverses dans les diodes intrinsèques des interrupteurs, il est nécessaire de réaliser les temps morts nécessaires pour éviter des chevauchements entre les interrupteurs du haut et du bas de chaque pont et donc des court-circuit. De plus, il faut considérer un transformateur réel et non idéal afin d'éviter un couplage parfait entre le primaire et le secondaire. Les inductances de fuite modifient le comportement du dispositif.

Le temps de conduction de chaque interrupteur est diminué afin de garantir des temps morts d'environ  $1[\mu s]$ .

Figure 54 : Temps mort entre les commandes de deux interrupteurs d'un même bras

Carreto Romain 49 / 93

## 4.3 Synthèse de la phase de conception

La phase de conception a permis de définir les sujets suivants :

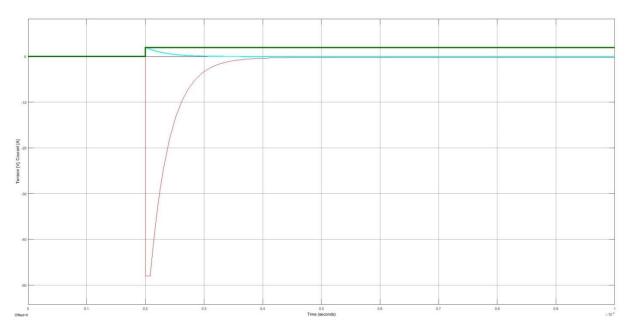

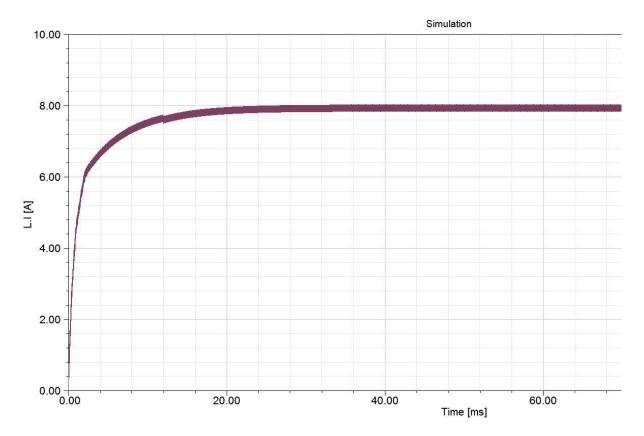

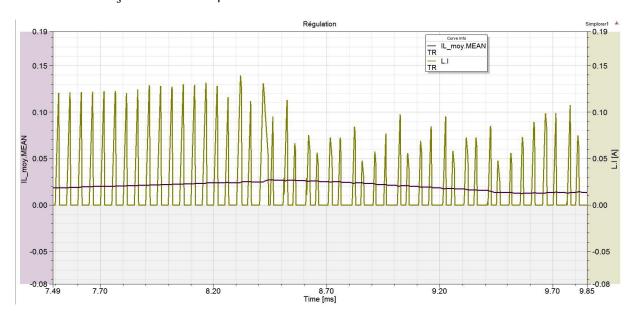

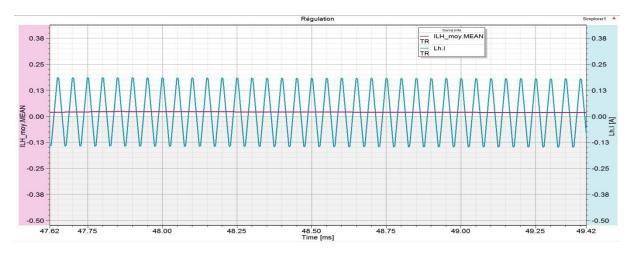

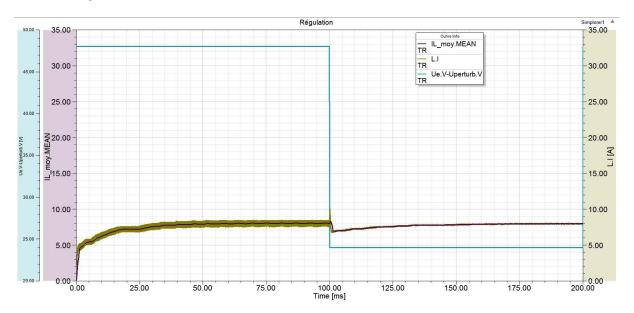

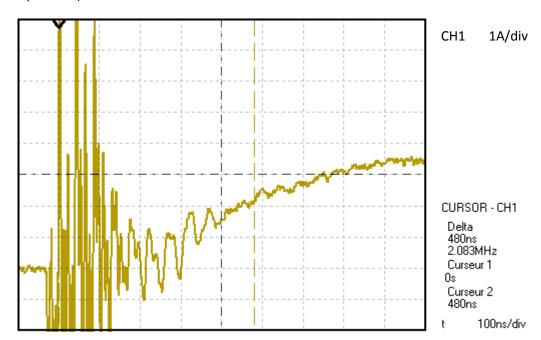

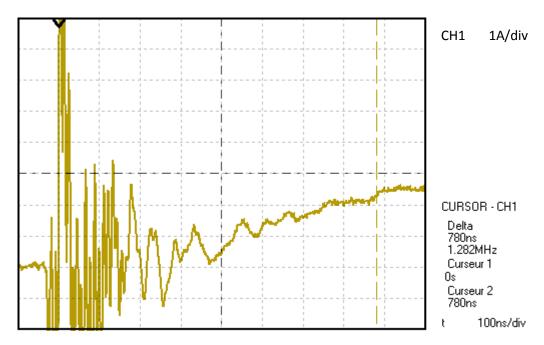

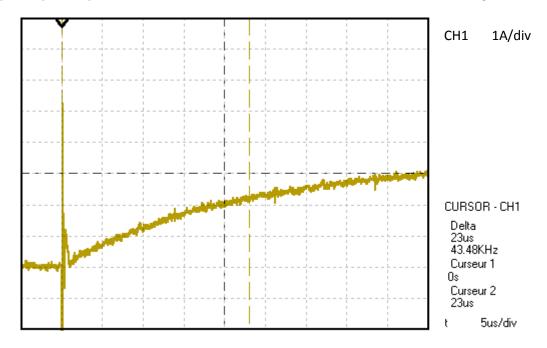

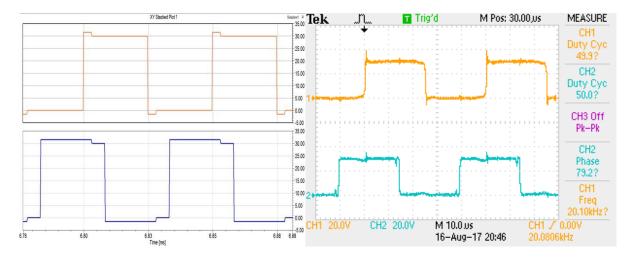

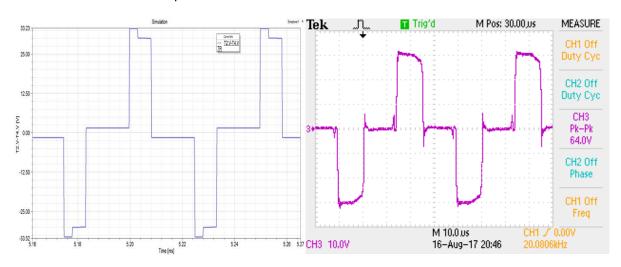

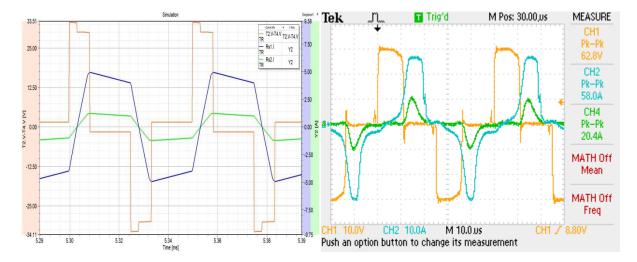

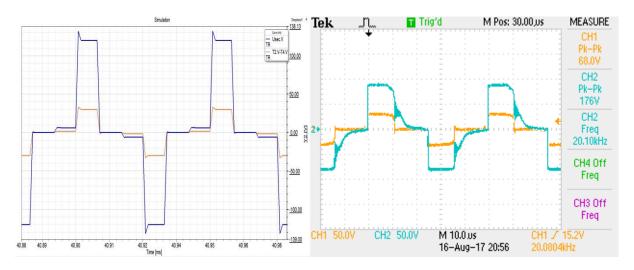

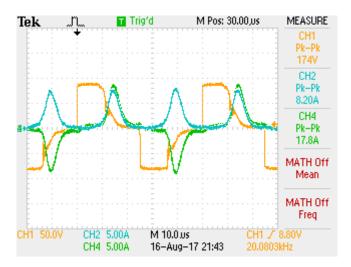

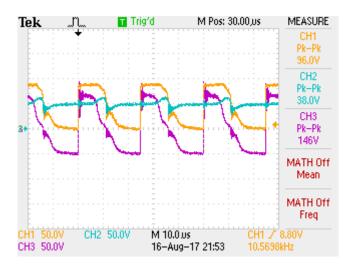

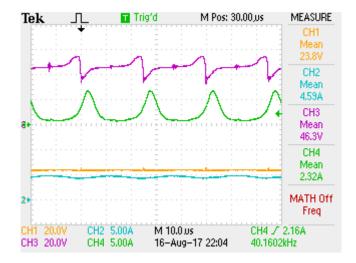

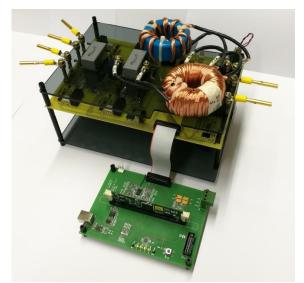

- Comportement du système en boucle ouverte